FPGA卷积神经网络手写数字识别 · 简易指南

0 项目简介

将训练好的卷积神经网络部署到开发板上,用摄像头采集黑底白字的数字,在显示屏中显示推理的数字,从而实现手写数字识别。

项目来自verimake的手写数字识别,视频演示点击此处。

1 环境配置

软件:Windows 10、TD5.6.5、vscode

硬件:EG4S20BG256开发板、VGA线、OV2640摄像头、显示屏

- 安装TD软件,版本号为5.6.5。

- 安装vscode。

- 安装插件

Verilog-HDL/SystemVerilog/Bluespec SystemVerilog、Verilog HDL、Verilog Snippet,以优化编程体验。

2 下载仓库

下载项目仓库

从verimake的手写数字识别仓库中,克隆下载仓库。

仓库层次主体如下图所示。source目录下中存放了需要用到的工程文件,其中al_ip文件夹中存放了安路ip核,rtl文件夹中存放了项目的所有verilog代码,sdc文件夹中存放了管脚约束文件,handwrite.al文件是TD软件创建的工程代码。

// 根目录

├── readme/

│ ├── ……

│ └── ……

│

└── sources/

├── al_ip/

├── doc/

├── weight_parameters(后续添加的)/

├── rtl/

├── sdc/

└── handwrite.al

下载权重文件

阅读readme.md,按照指示从该仓库中下载权重文件,在source目录下创建weight_parameters文件夹,并按照卷积网络的不同层进行分类,如:

weight_parameters/

├── con1/

│ ├── weight.txt

│ └── bias.txt

├── conv2/

│ ├── weight.txt

│ └── bias.txt

├── fc/

│ ├── weight.txt

│ └── bias.txt

└── mnist_input/

└── 表示0~10的txt文件,挑顺眼的就行

修改代码

verilog代码中,使用了$readmemh()读入来权重文件,其路径必须为权重文件的绝对路径,因此需要对原码做出修改,具体如下:

在conv1.v、conv2.v、full_layer.v、output_layer.v四个文件中,将所有的$readmemh()路径修改为自己路径下权重文件的绝对路径。

// 原路径

$readmemh("D:/Anlogic/code/my_code/veri/SPARKROAD/Handwritten/sources/weight_parameters/conv1/conv1_weight_1.txt", weight_1);

3 上板验证

硬件连接

连接VGA接口与独立的显示屏,插入OV2640摄像头,连接下载器与电脑,如下图所示:

工程建立

可以选择直接打开handwrite.al工程文件。但若报错的话,也可以新建工程后一步一步导入,具体步骤如下(可参考基于TD5.6.5与vscode的FPGA简易开发教程——以多路选择器为例。):

- 新建一个名为

handwrite.al的工程文件。

- 单击

Compile Order,导入rtl目录下的所有verilog文件,作为设计文件。

- 单击

IP Files,导入整个al_ip文件夹,作为ip核。

- 单击

Project hierarchy,将test_camera.v文件设为顶层文件。

- 单击

Project hierarchy下的constraint_1(active),导入sdc文件夹下的SparkRoad.adc作为管脚约束。

- 完成硬件连接。

- 点击编译,将生成的比特流下载到开发板中。

上板验证

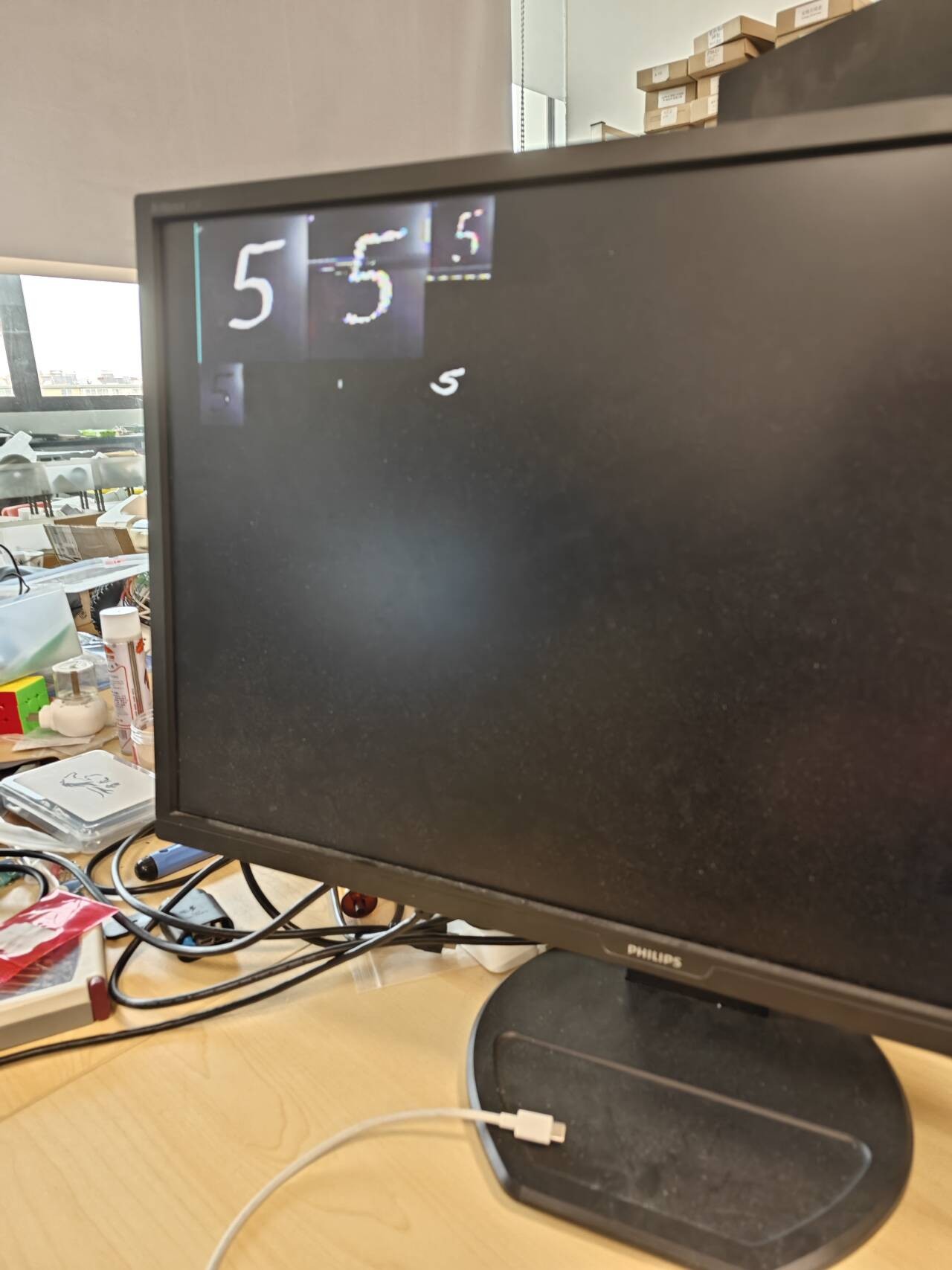

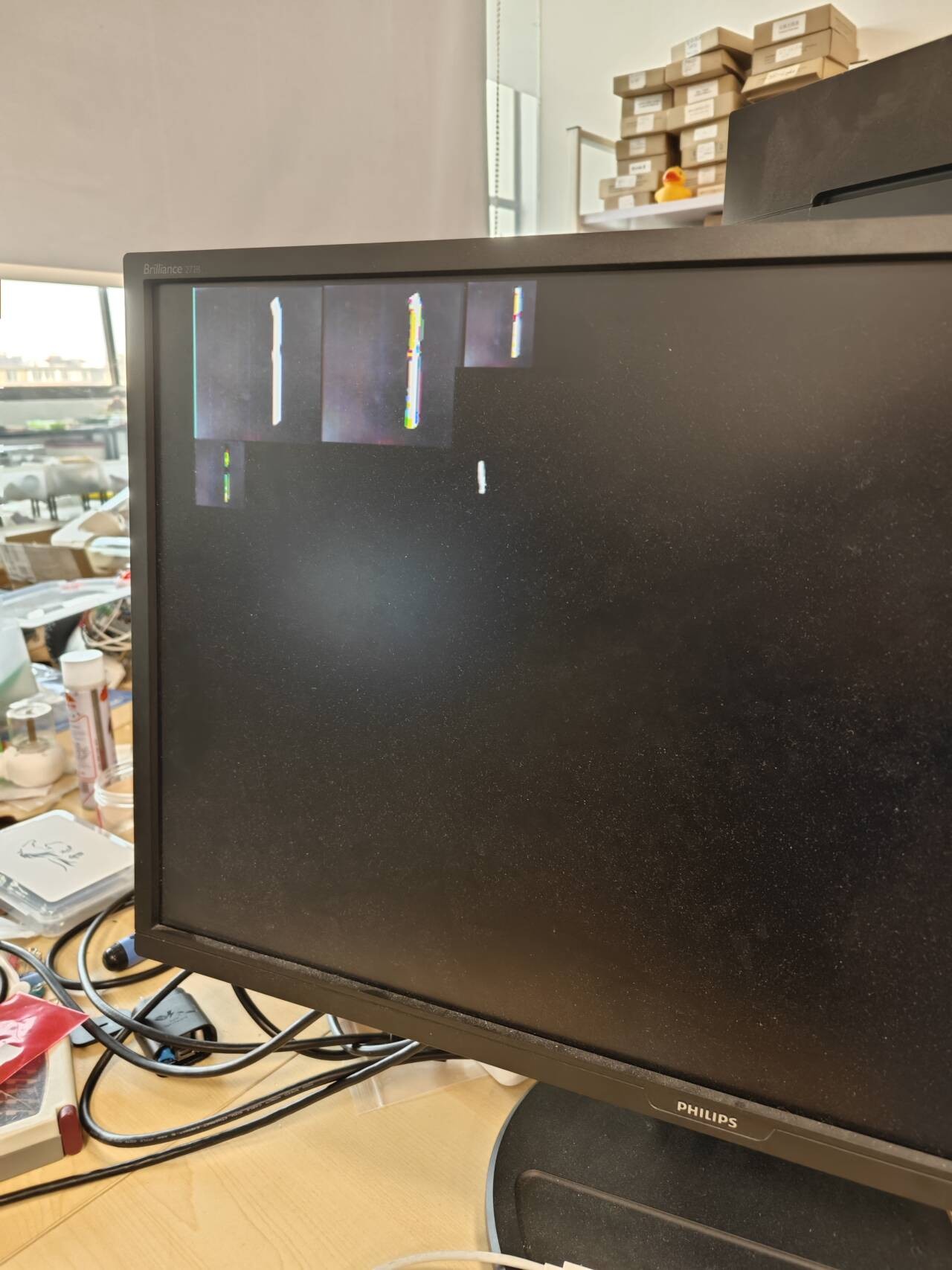

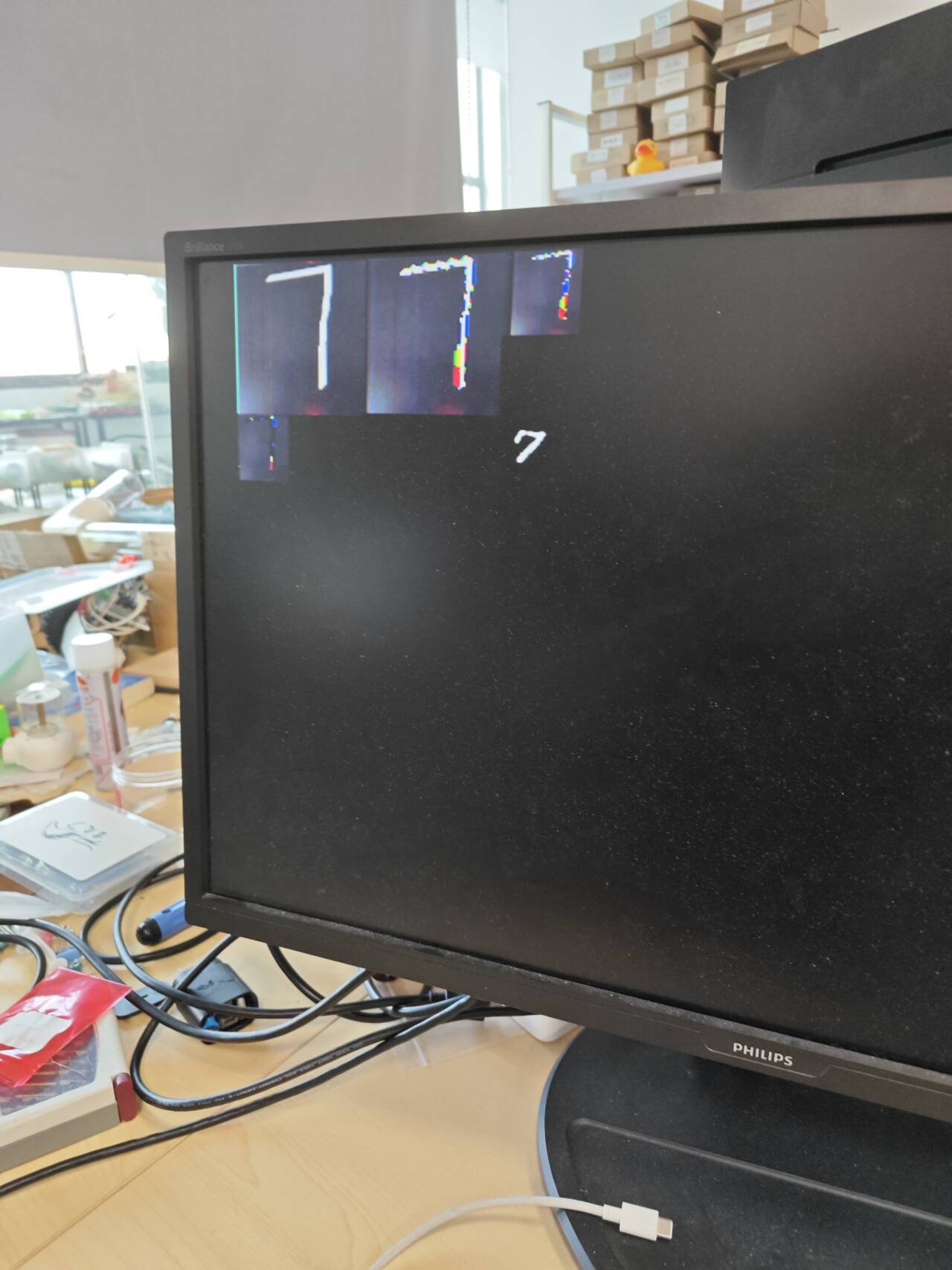

用黑底白字的阿拉伯数字作为输入,对准摄像头,观察显示屏的是否能正确识别数字。

举例如下:

- 采用win10的的画图功能,绘画出不同的黑底白字数字,如下图所示。

- 观察显示屏是否能正确识别,如下图所示。多次重复两个步骤

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1