基于TD5.6.5与vscode的FPGA简易开发教程——以多路选择器为例

1 环境搭建

软件:Windows 10、TD5.6.5、vscode

硬件:EG4S20BG256

2 实现的功能

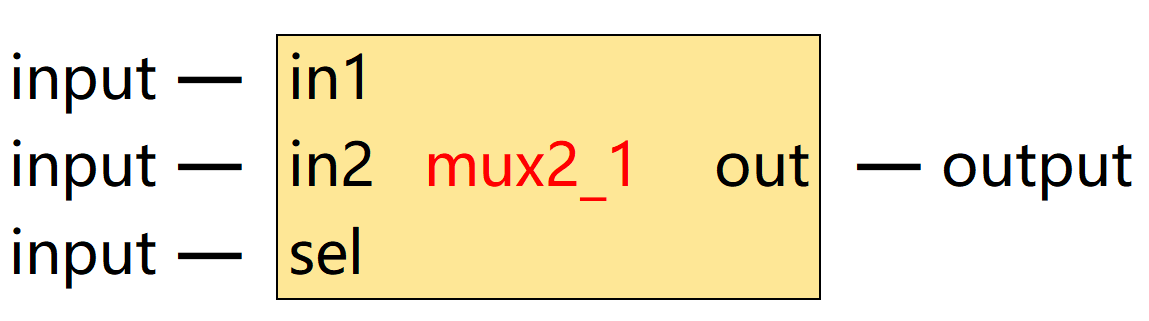

| Port name | Direction | Type | Description |

|---|

| in1 | input | wire | 输入1 |

| in2 | input | wire | 输入2 |

| sel | input | wire | 选择输入1或2 |

| out | output | wire | 输出 |

如图,根据拨码开关in1、in2、sel来控制蓝灯的亮灭。当sel为1时,in1控制灯的亮灭,in2对灯亮灭没有影响;当sel为0时同理。

3 程序设计

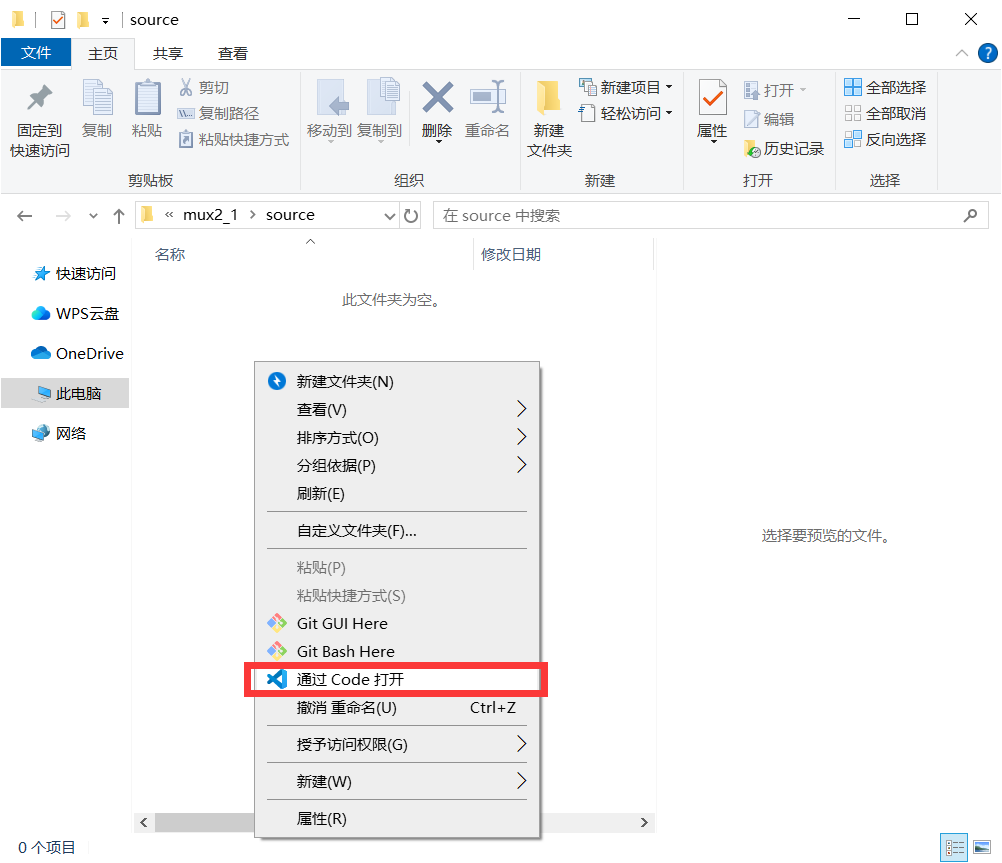

新建工程文件

新建用于存放整个工程的文件夹(无中文路径),命名为mux2_1;在该文件下新建用于存放工程代码的文件夹,命名为source。在source文件夹内右键,选择通过 Code 打开,进入vscode界面。

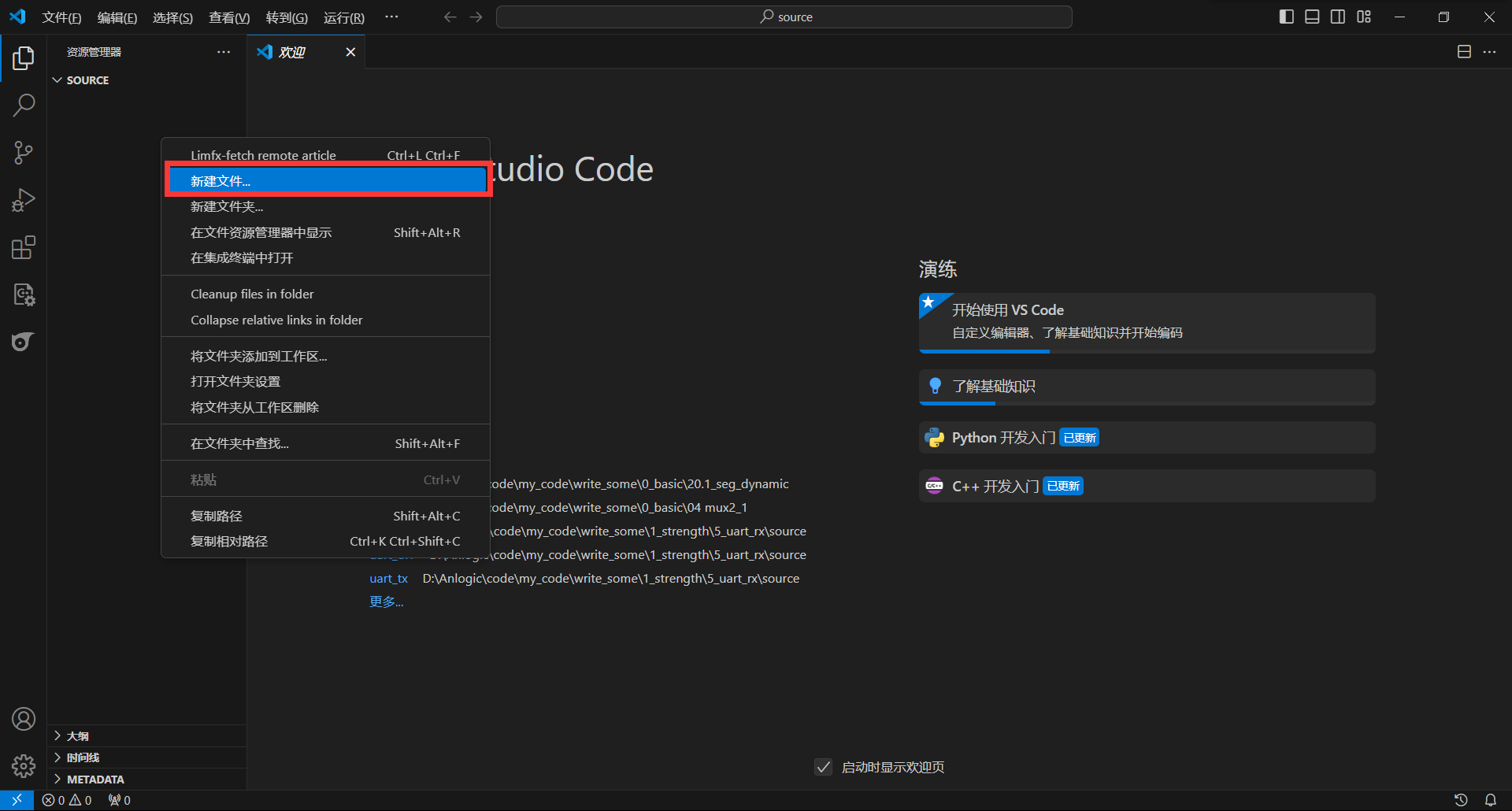

进入vscode中,在资源管理器界面右键,选择新建文件,命名为mux2_1.v。

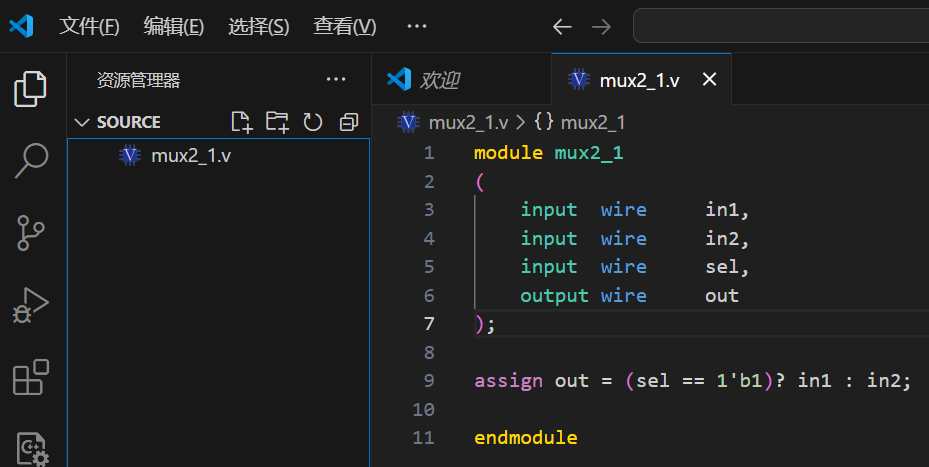

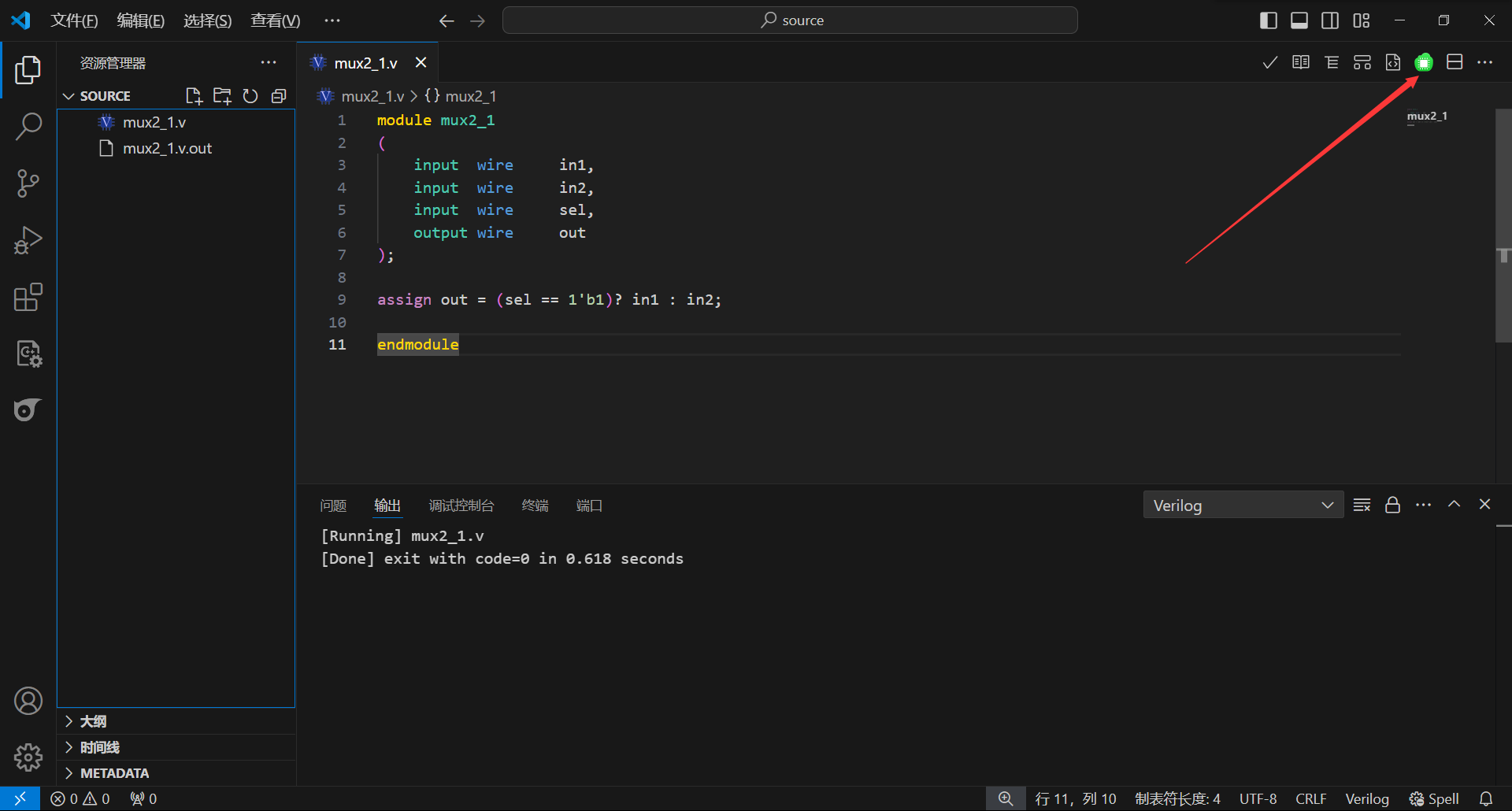

编写设计文件

在mux2_1.v内,编写设计文件。这里编写了多路选择器程序,通过sel的值来输出in1或in2的值。

module mux2_1

(

input wire in1,

input wire in2,

input wire sel,

output wire out

);

assign out = (sel == 1'b1)? in1 : in2;

endmodule

编译

点击右上角绿色按钮,如果编译无误,则在左侧的资源管理器界面生成了一个mux2_1.v.out文件。

4 波形仿真

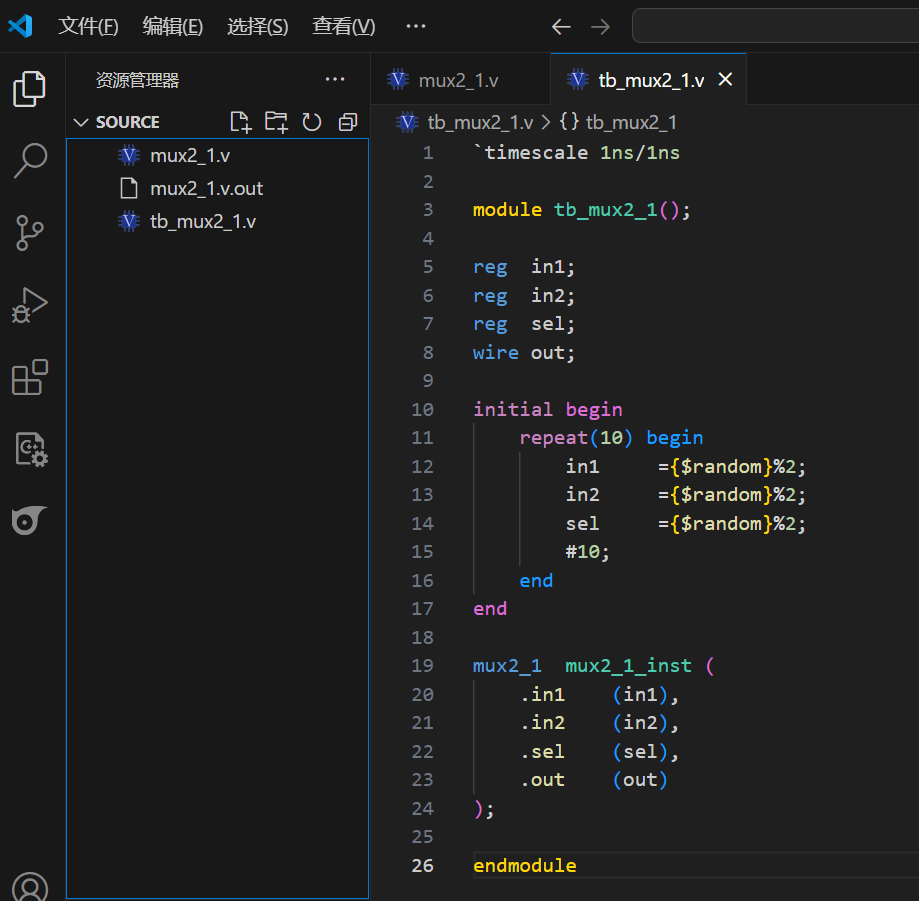

编写验证文件

在资源管理器界面右键,选择新建文件,命名为tb_mux2_1.v,并在其中编写验证文件。这里每隔10ns随机赋予in1、in2、sel的值,则out的值将随之变化。

`timescale 1ns/1ns

module tb_mux2_1();

reg in1;

reg in2;

reg sel;

wire out;

initial begin

repeat(10) begin

in1 ={$random}%2;

in2 ={$random}%2;

sel ={$random}%2;

#10;

end

end

mux2_1 mux2_1_inst (

.in1 (in1),

.in2 (in2),

.sel (sel),

.out (out)

);

endmodule

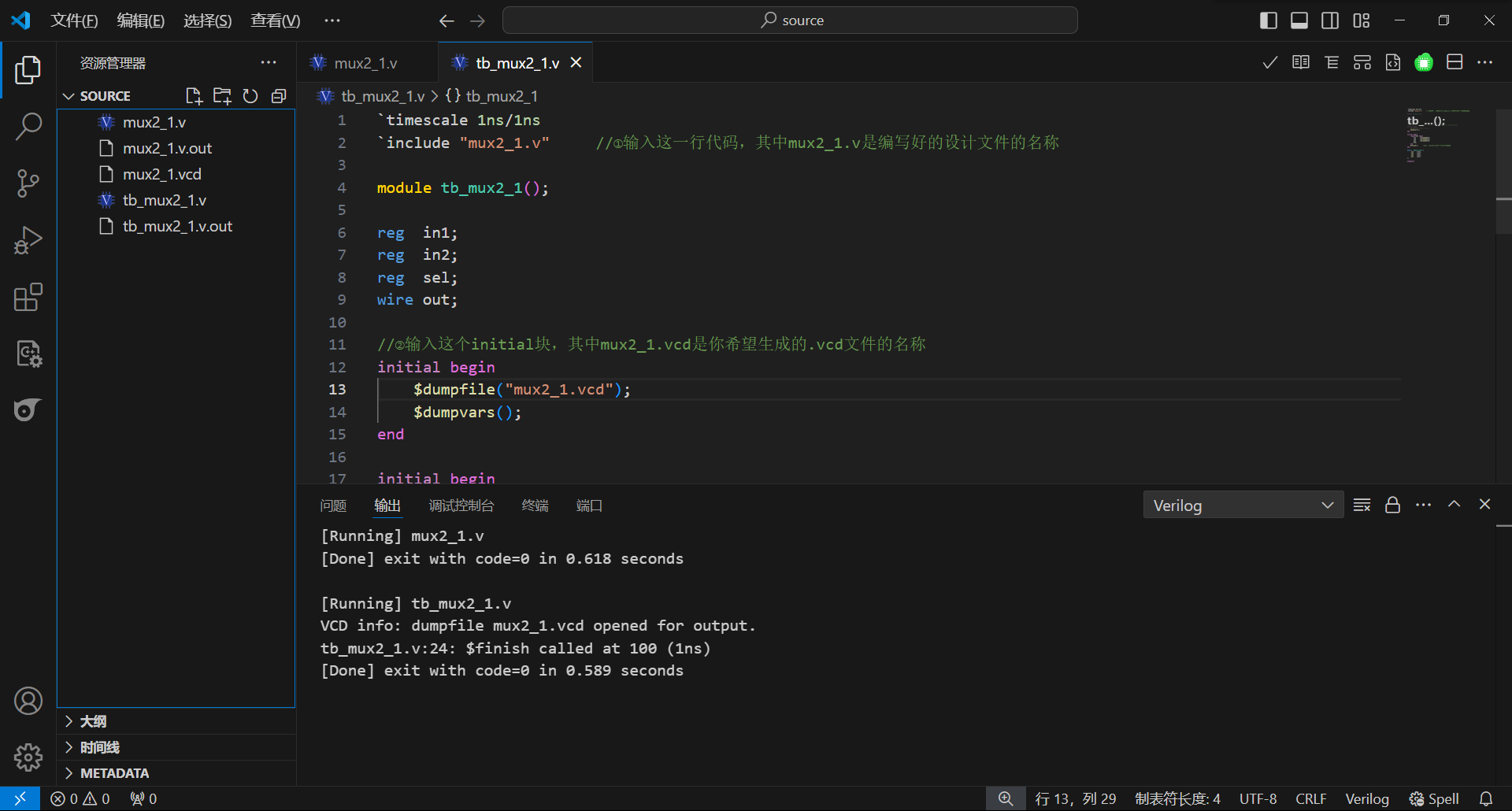

生成.vcd文件

由于波形仿真采用了插件WaveTrace,因此需要在上面已经写好的tb文件中额外添加部分内容,以此产生.vcd文件,具体如下:

注意,tb文件中必须要有finish();,否则程序非常有可能结束不了,此时需要在任务管理器中,手动结束vvp.exe进程。

`timescale 1ns/1ns

`include "mux2_1.v" //①添加这一行代码,其中mux2_1.v是编写好的设计文件的名称

module tb_mux2_1();

reg in1;

reg in2;

reg sel;

wire out;

//②添加这个initial块,其中mux2_1.vcd是你希望生成的.vcd文件的名称

initial begin

$dumpfile("mux2_1.vcd");

$dumpvars();

end

initial begin

repeat(10) begin

in1 ={$random}%2;

in2 ={$random}%2;

sel ={$random}%2;

#10;

end

$finish(); //③添加finish(),防止程序结束不了。

end

mux2_1 mux2_1_inst (

.in1 (in1),

.in2 (in2),

.sel (sel),

.out (out)

);

endmodule

完成添加后,点击右上角绿色按钮,如果编译无误,在左侧的资源管理器界面生成了一个tb_mux2_1.v.out文件、一个mux2_1.vcd文件。

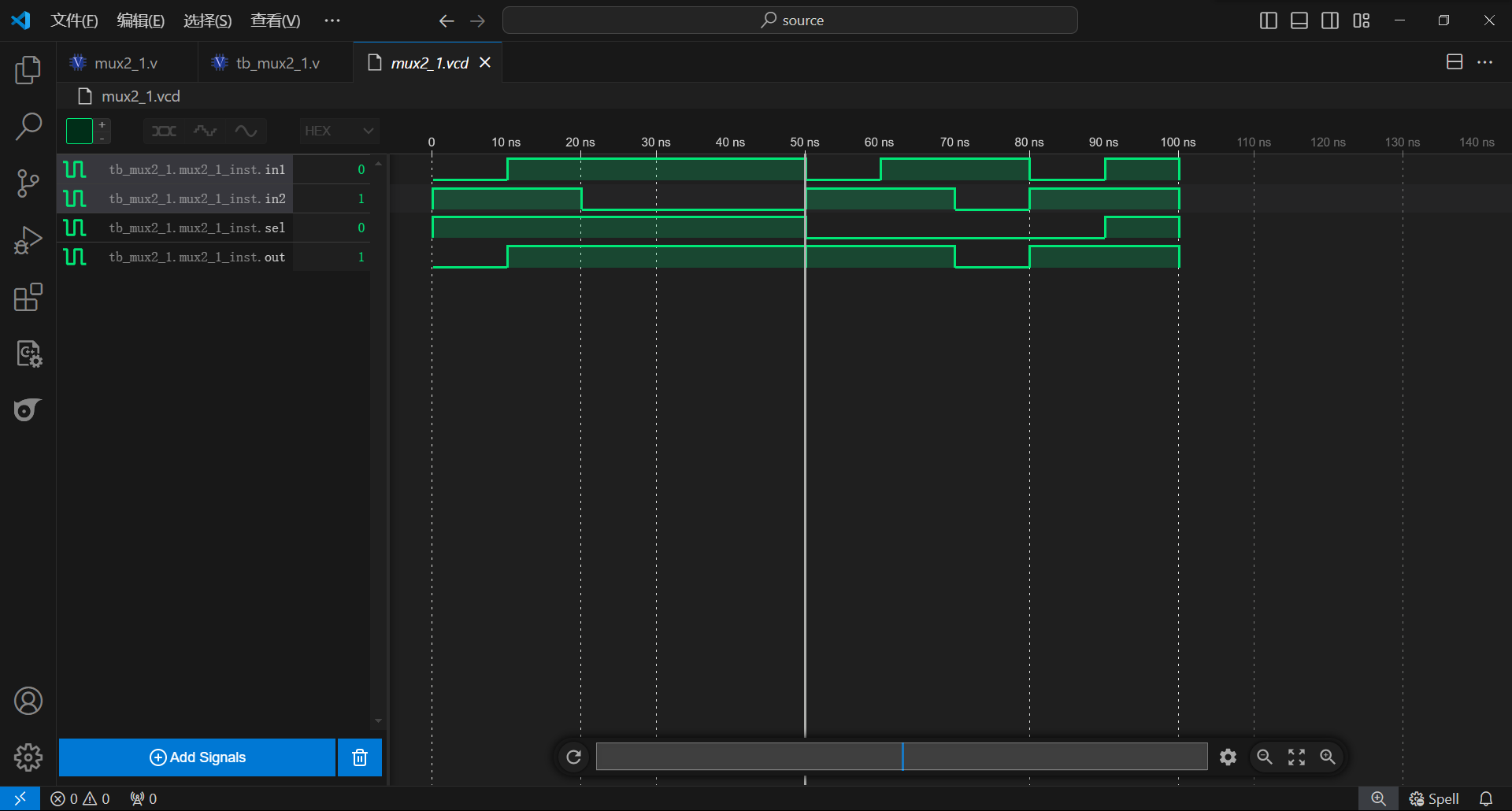

查看波形

双击打开mux2_1.vcd文件,点击Add Signals,依次双击添加四个信号。

查看生成的波形是否符合设计的逻辑。当sel为1时,out仅和in1有关,且输出in1的波形;当sel为0时,out仅和in2有关,且输出in2的波形。因此仿真波形与设计逻辑相符。

5 上板验证

在TD 5.6.5软件中,利用FPGA芯片EG4S20BG256进行上板验证。

TD软件的使用

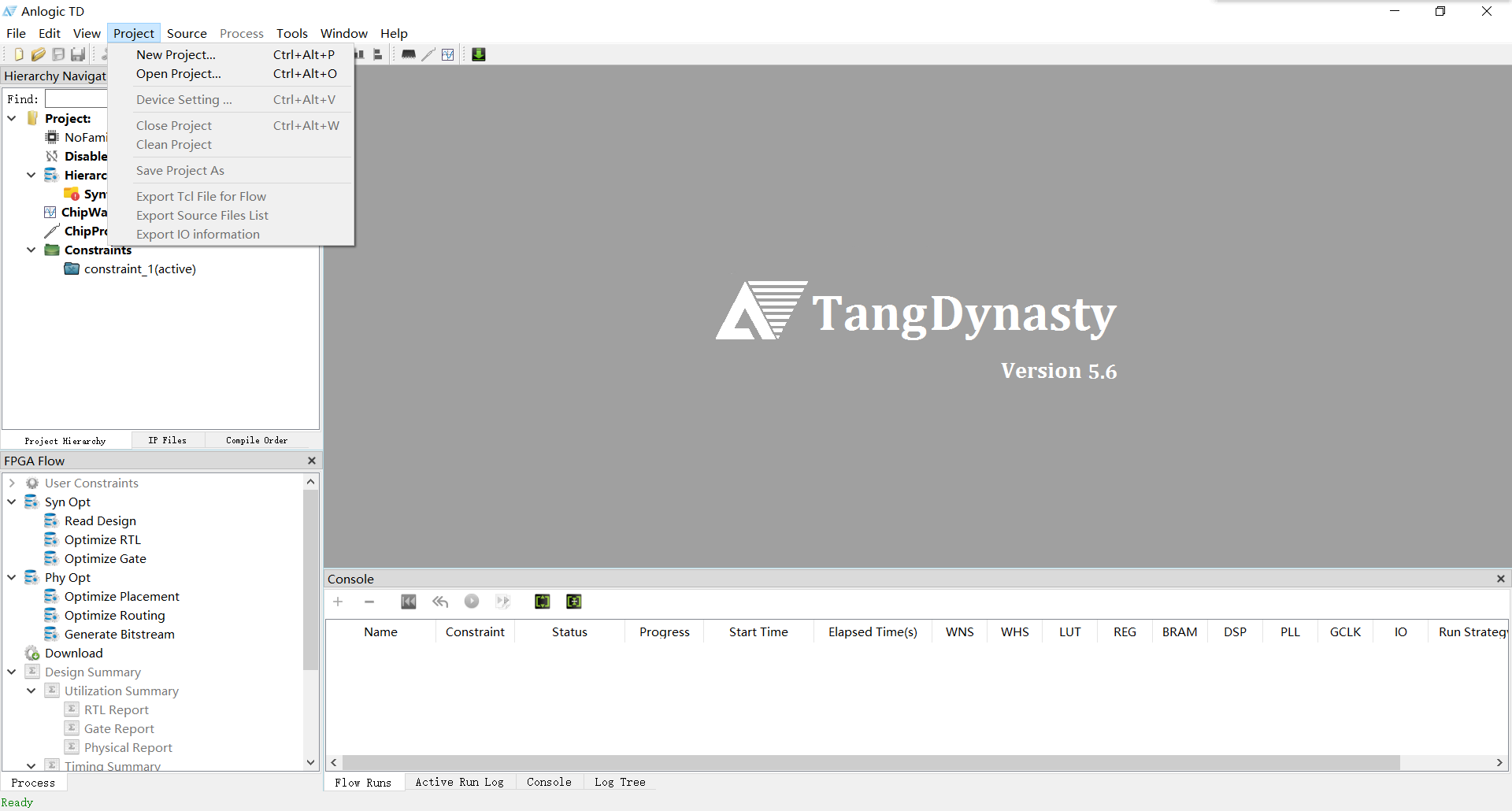

打开TD5.6.5,单击Project,选择New Project。

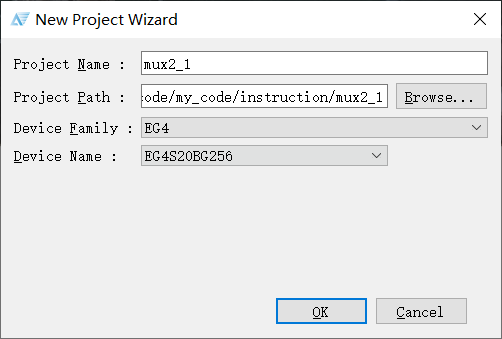

项目文件命名为mux2_1,路径选择mux2_1(即与source文件夹同一级),芯片型号如图选择。

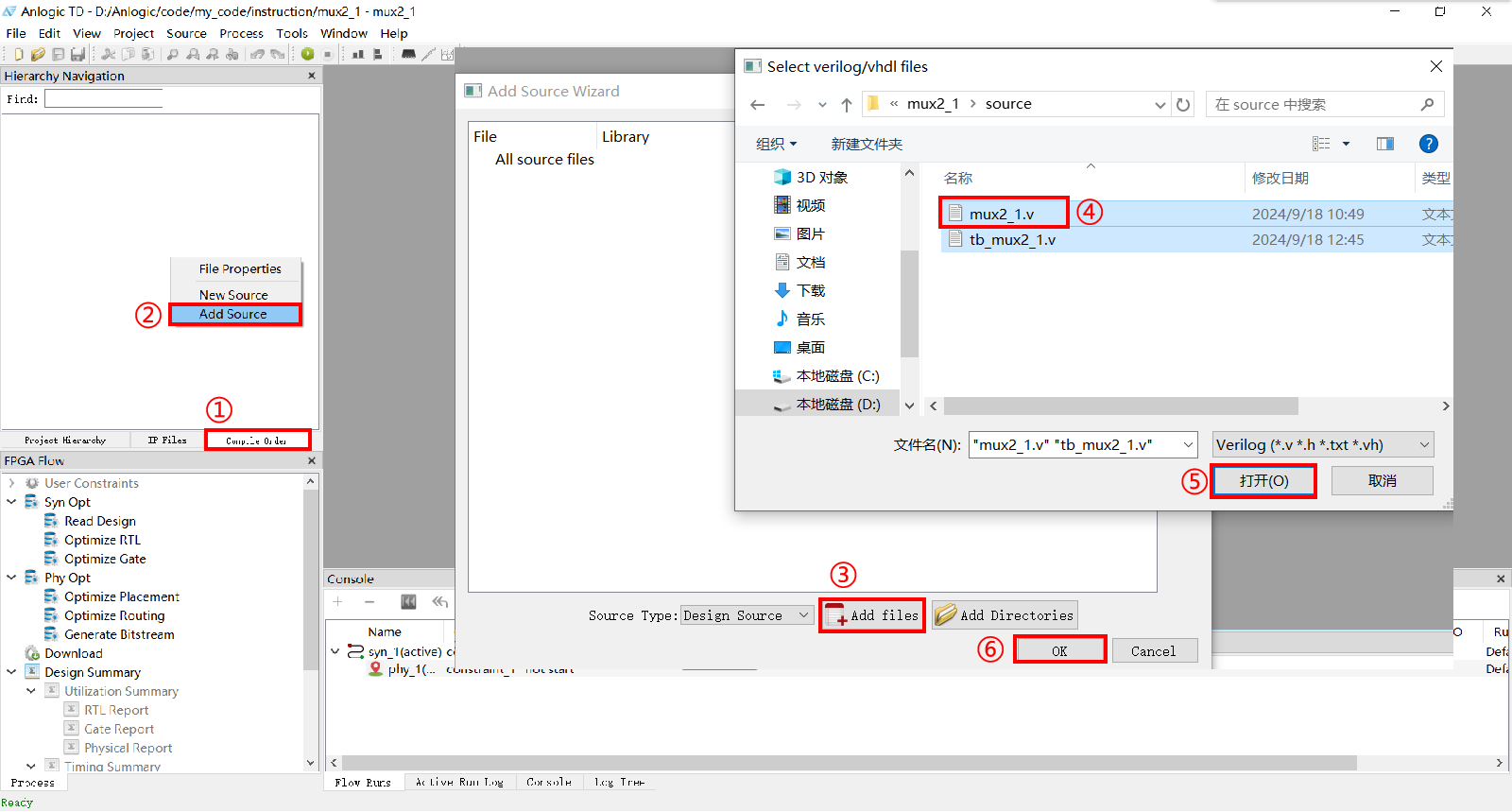

单击Compile Order,右键,选择Add Source,选择Add files,进入source文件夹,只选中设计文件mux2_1.v,单击打开,单击OK。

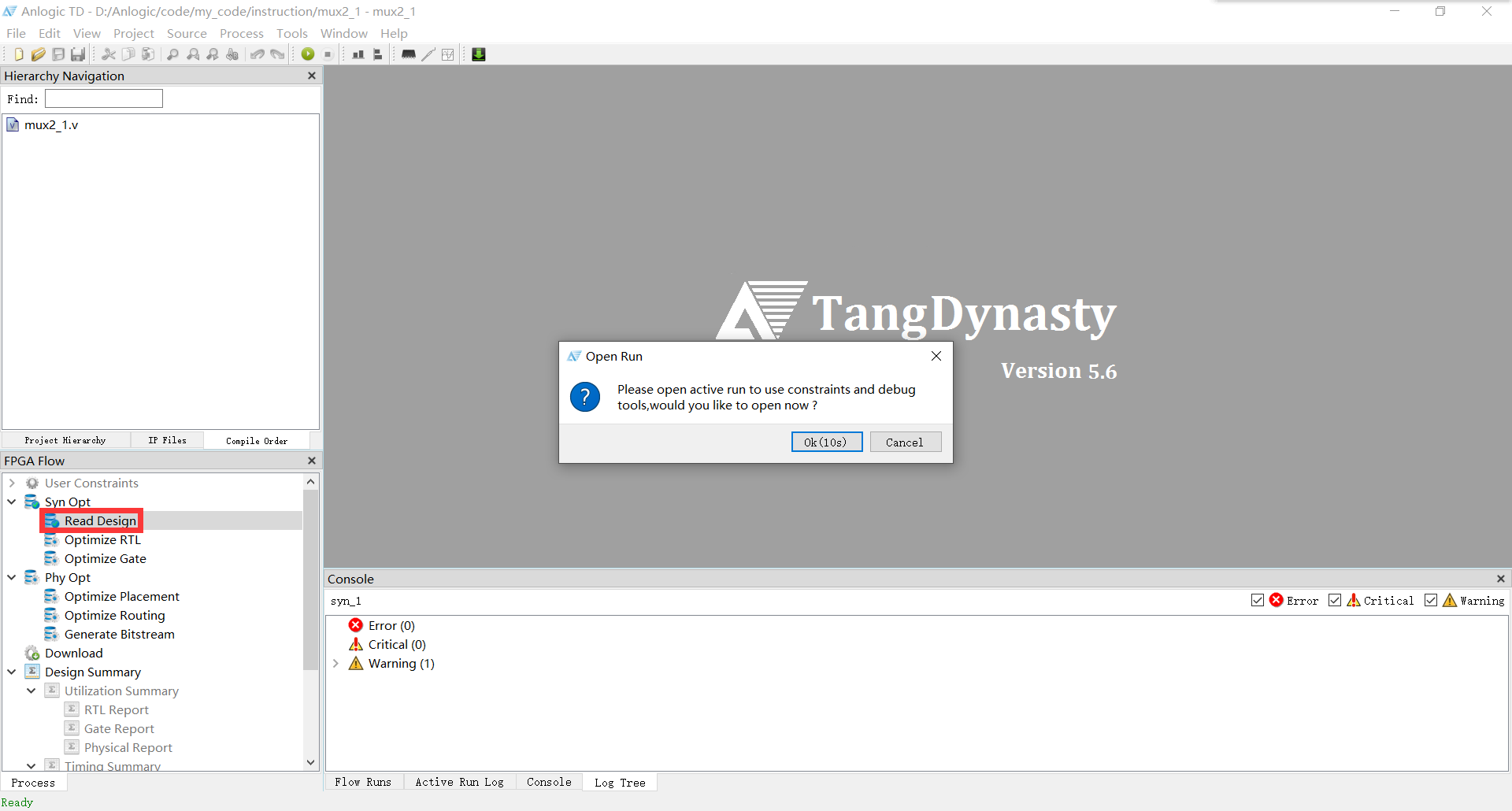

双击Read Design,若设计文件正确无误,点击OK。

分配管脚

为端口信号分配管脚:这里采用三个拨码开关,分别模拟输入in1、in2、sel的变化;输出采用RGB的蓝灯,观察不同sel值时蓝灯的变化。

| 端口信号 | 引脚 |

| :-------: | :-----------: |

| in1,输入 | R14,拨码开关 |

| in2,输入 | T15,拨码开关 |

| sel,输入 | R15,拨码开关 |

| out,输出 | N16,RGB蓝灯 |

怎么没有表格,什么情况

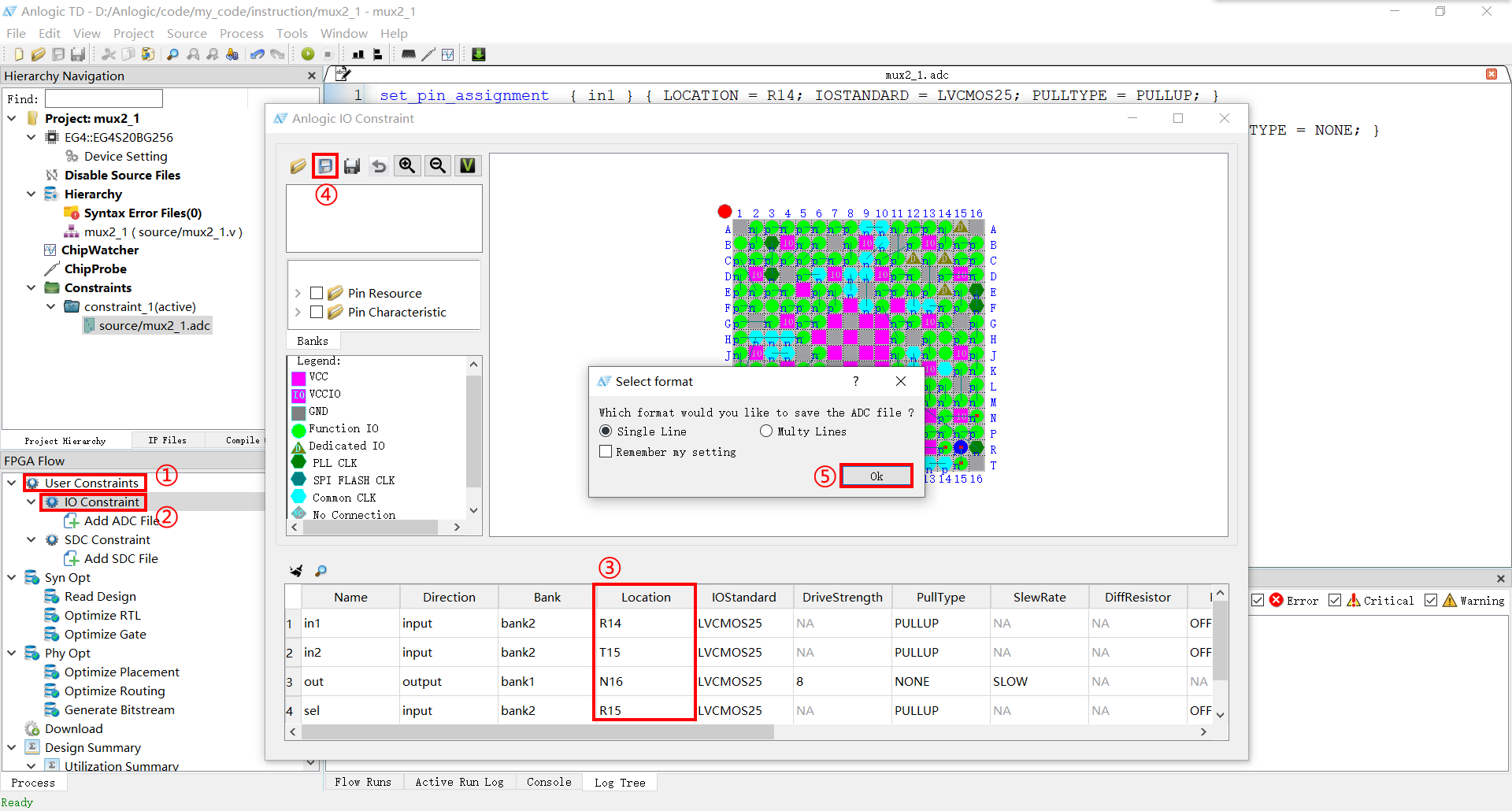

具体分配管脚的步骤如下:双击User Constraints,双击IO Constraints,在Location一览分配管脚。

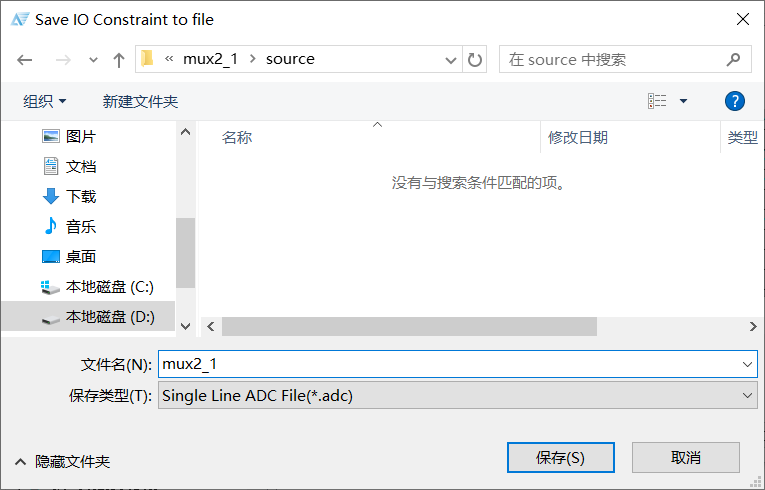

将管脚约束保存为.adc文件,单击保存后,单击YES,将该约束添加到了TD中。

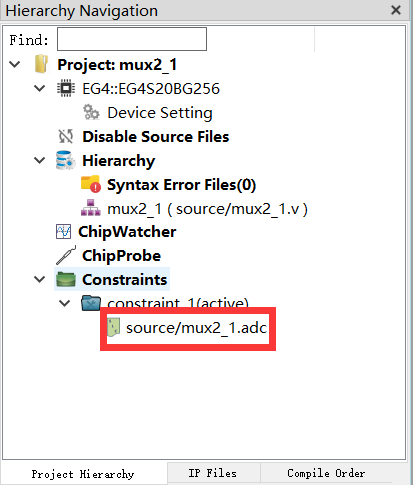

如图,显示刚保存的约束文件,因此成功将约束添加到工程中。后续想修改管脚时可以重新在IO Constraints中分配,也可以直接修改.adc文件。

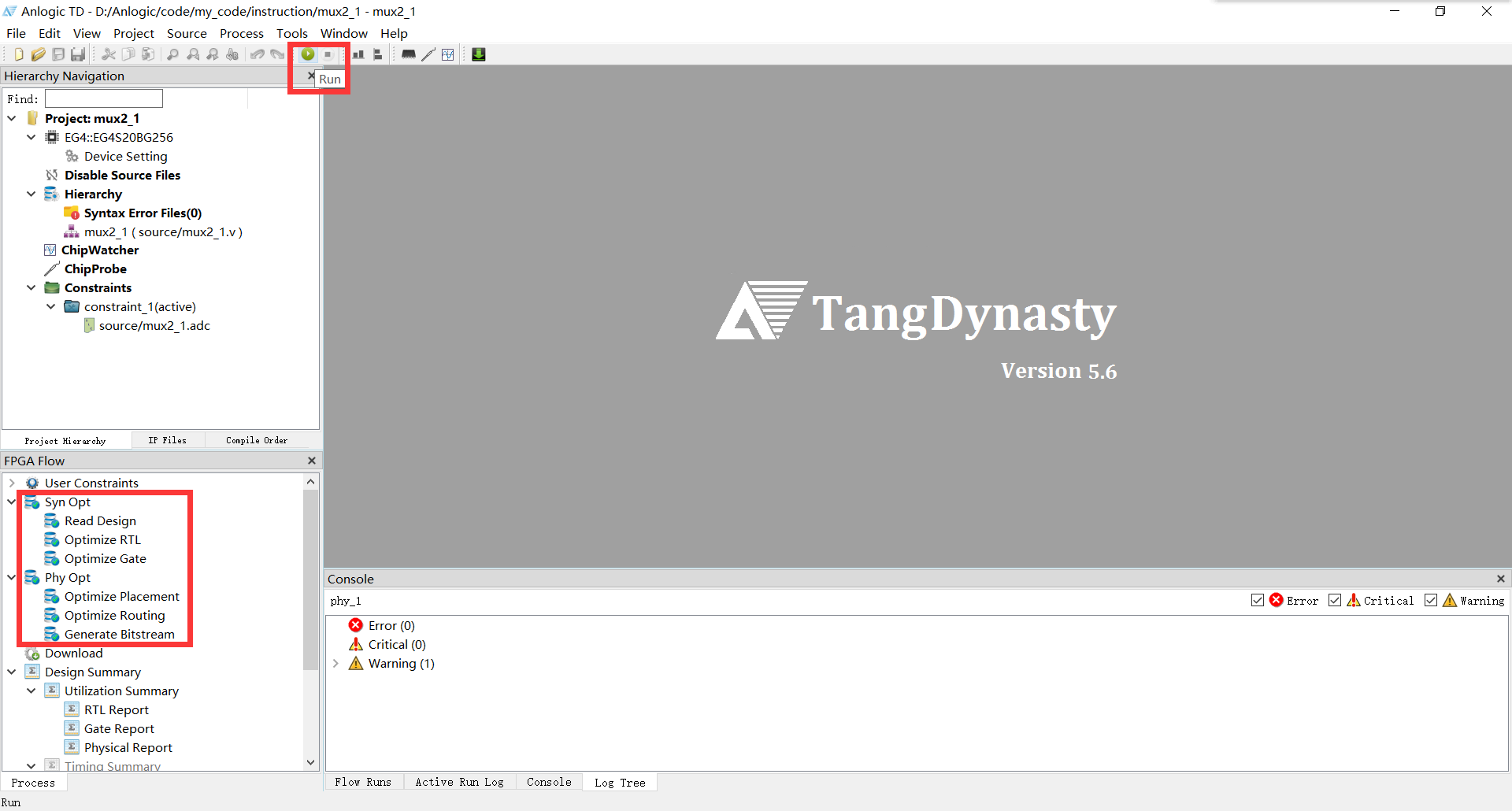

回到TD页面,单击绿白色的run按钮,会依次执行左侧红框中的步骤,直至全打上勾,表明已成功生成比特流文件(具体在mux2_1\mux2_1_Runs\best_result文件夹中),后续可将程序烧录到FPGA中。

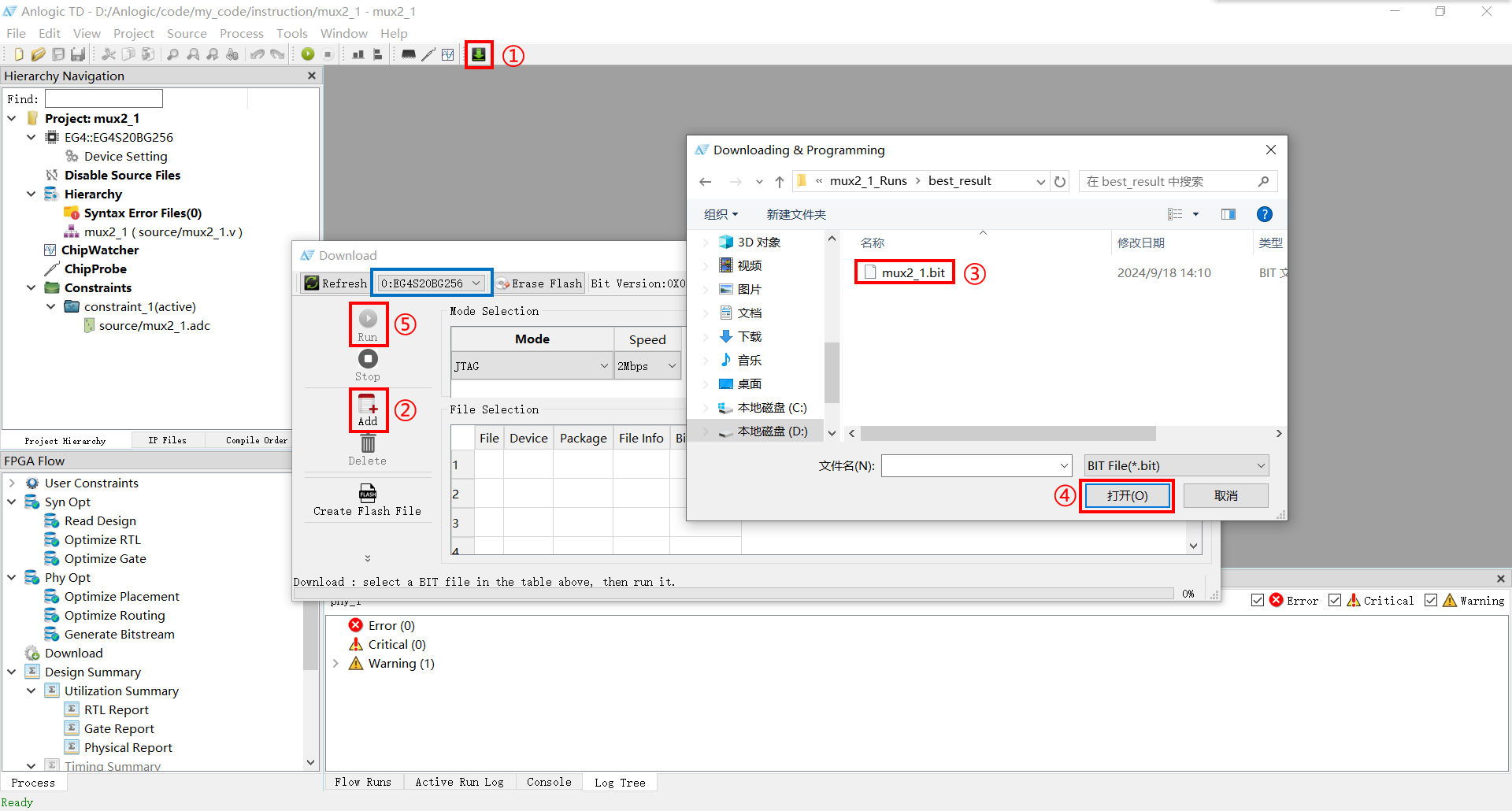

烧录

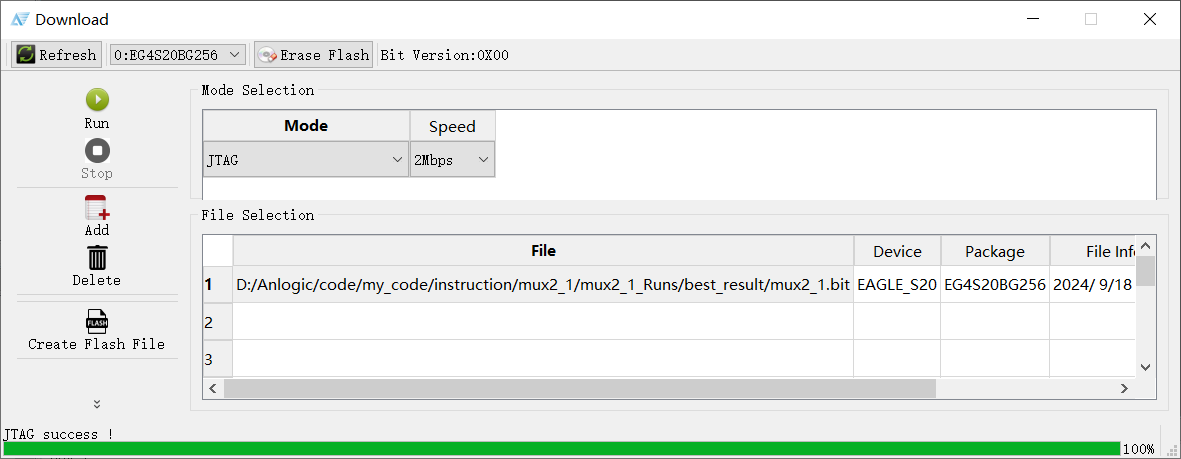

拿出下载器,两端分别连接FPGA与电脑。点击黑绿色的download按钮,进入下载界面,若如下图的蓝框中显示具体芯片型号,则说明连接成功。点击Add,在mux2_1_Runs文件夹的best_result文件夹中选择mux2_1.bit文件。

单击Run,等待一小段时间,等进度条达100%时烧录完成。

上板验证

将sel拨动到1,发现此时蓝灯的亮灭只与in1有关,in1为0时蓝灯亮,为1时蓝灯灭;拨动in2不影响蓝灯的亮灭

再将sel拨动到0,发现此时蓝灯的亮灭只与in2有关,in2为0时蓝灯亮,为1时蓝灯灭;拨动in1不影响蓝灯的亮灭。

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1