注:该工程需要使用6.0以上的新版TD

1. 工程说明

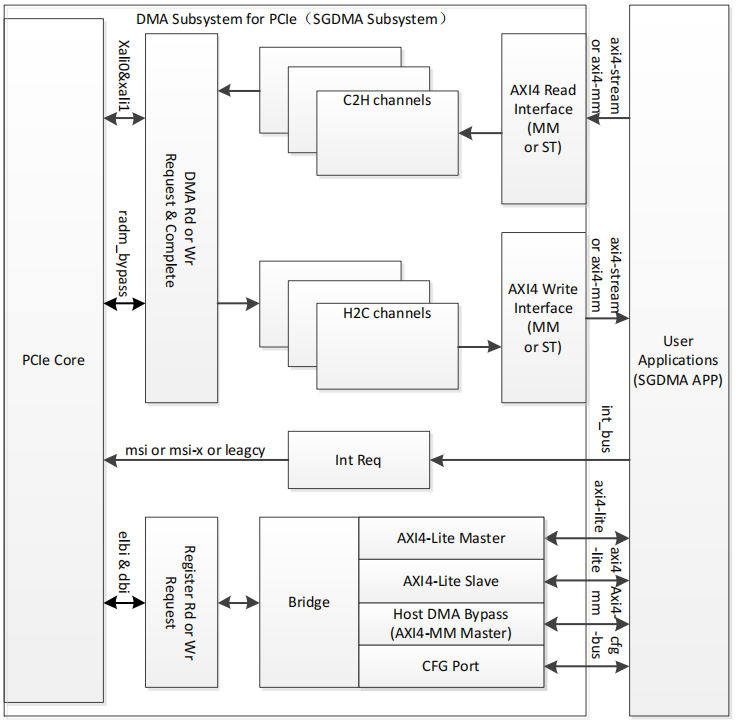

SGDMA是一个 PCIe2AXI4 系列接口的高性能DMA。样例工程包含两个模块,sgdma_subsys模块和sgdma_app模块,其中sgdma_subsys模块是实现了PCIe DMA子系统和PCIe to AXI系列接口转化的模块,sgdma_app模块是用于测试的app模块。DMA子系统框图如下所示:

DMA模块的端口描述如下:

| app_auxclk | 输入 | 提供给PCIe硬核的常在辅助时钟,时钟频率为25MHZ或50MHZ |

|---|

| user_clk | 输出 | PCIe core时钟,用于驱动用户接口 |

| app_power_up_rst_n | 输入 | PCIe core输入复位,当前连接到金手指的复位信号上 |

| user_resetn | 输入 | PCIe core输出用户复位,低电平有效 |

| | |

| user_link_up | 输出 | PCIe core link up信号 |

| ltssm_state | 输出 | PCIe core ltssm状态机信号 |

| | |

| m_axis* | | AXI_ST master接口 |

| s_axis_* | | AXI_ST slave接口 |

| cfg_mgmt* | | 读写PCIe控制器配置空间 |

| m_axil_* | | AXI_lite master接口,读写user寄存器 |

| s_axil_* | | AXI_lite slave接口,读写dma寄存器 |

2. 上板测试说明

该PCIE需要在Linux上位机中测试,推荐使用Ubuntu 20.04或其它较新的Linux发行版,否则可能存在一些软件编译问题。将PH1a开发板烧录完成并接入主板,确保在上位机启动前烧录bit流。如果在烧录PH1a之后再重启电脑,切记先关机再开机,而不是重启,否则主板可能不检测新的PCIe设备。

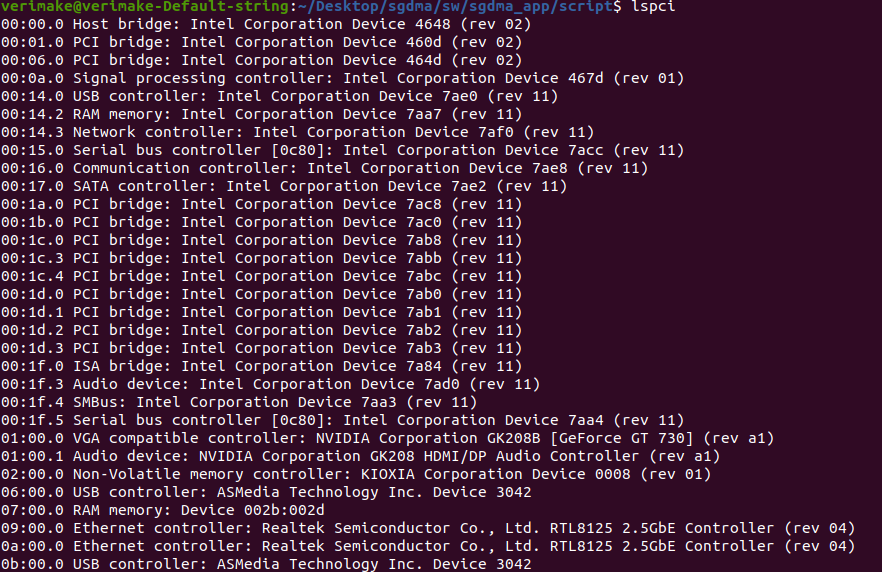

启动系统后在终端lspci查询PCIe设备,能见到类似列表。寻找设备RAM memory device (默认的设备号是1ebd:abcd)。

获得root权限,进入到anlogic_pcie_drv目录,执行make进行编译,然后执行insmod anlogic_pci.ko安装驱动

进入到anlogic_pcie_app/src目录,使用make编译用户函数

进入到anlogic_pcie_app/script目录,使用命令./chmod +x *给目录中所有文件可执行权限。

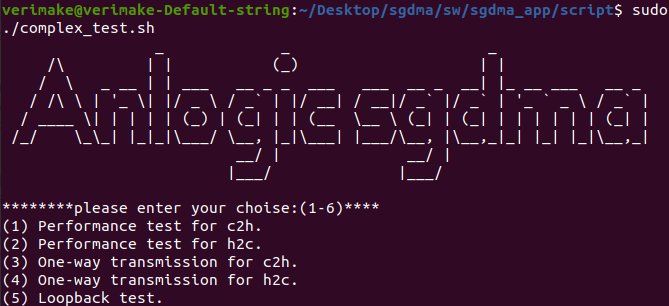

在anlogic_pcie_app/script目录下,是用命令./complex_test.sh进行功能测试。上位机软件画面如下:

不同项目的功能分别为:

Performance test for c2h: 用于 C2H 方向测速。

Performance test for h2c:用于 H2C 方向测速。

One-way transmission for c2h: 用于测试 C2H 方向数据传输。

One-way transmission for h2c: 用于测试 H2C 方向数据传输。

Lookback test: 用于数据环回测试。

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1