PH1A DDR IP 说明与创建

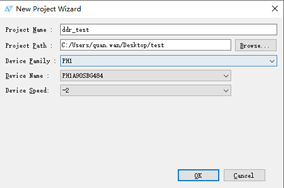

创建工程Project – New Project

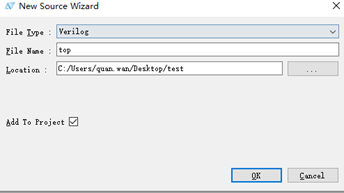

创建顶层文件Source –New Source

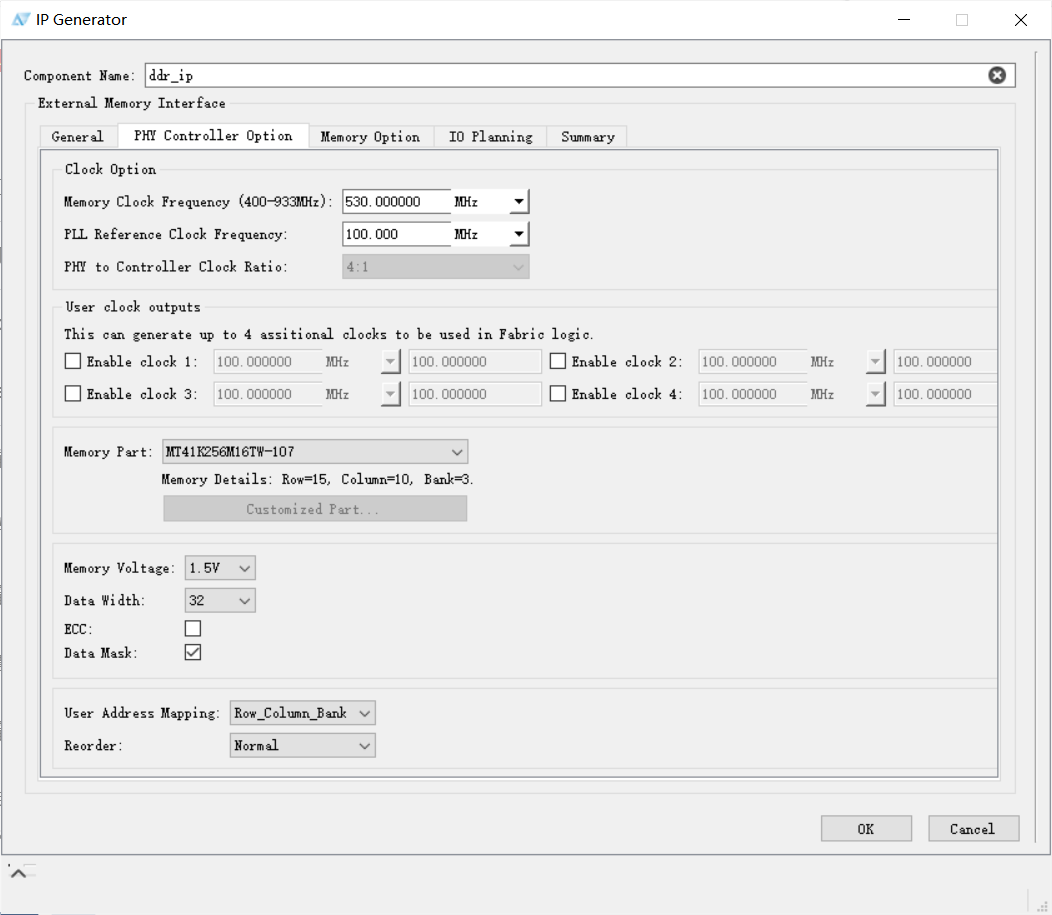

创建ddr ip,Tools – ip Generator - 输入名称 - DDR3/DDR4 SDRAM,选择DDR3的选项。在Controller/PHY Mode中,选择Standard PHY为仅PHY模块,DFI接口;选择MC + PHY则包含内存控制器(MC),可以位置为MC naive接口或AXI接口。在 TD 5.6.4之前的版本中,不支持创建包含MC的DDR ip,需要手动添加内存控制器模块,如 https://verimake.com/d/458-ph1a-ddruart-loop 中,控制器IP是额外添加到工程的。

修改输入时钟和需要的生成时钟频率,选择图中的颗粒,选中电压和位宽

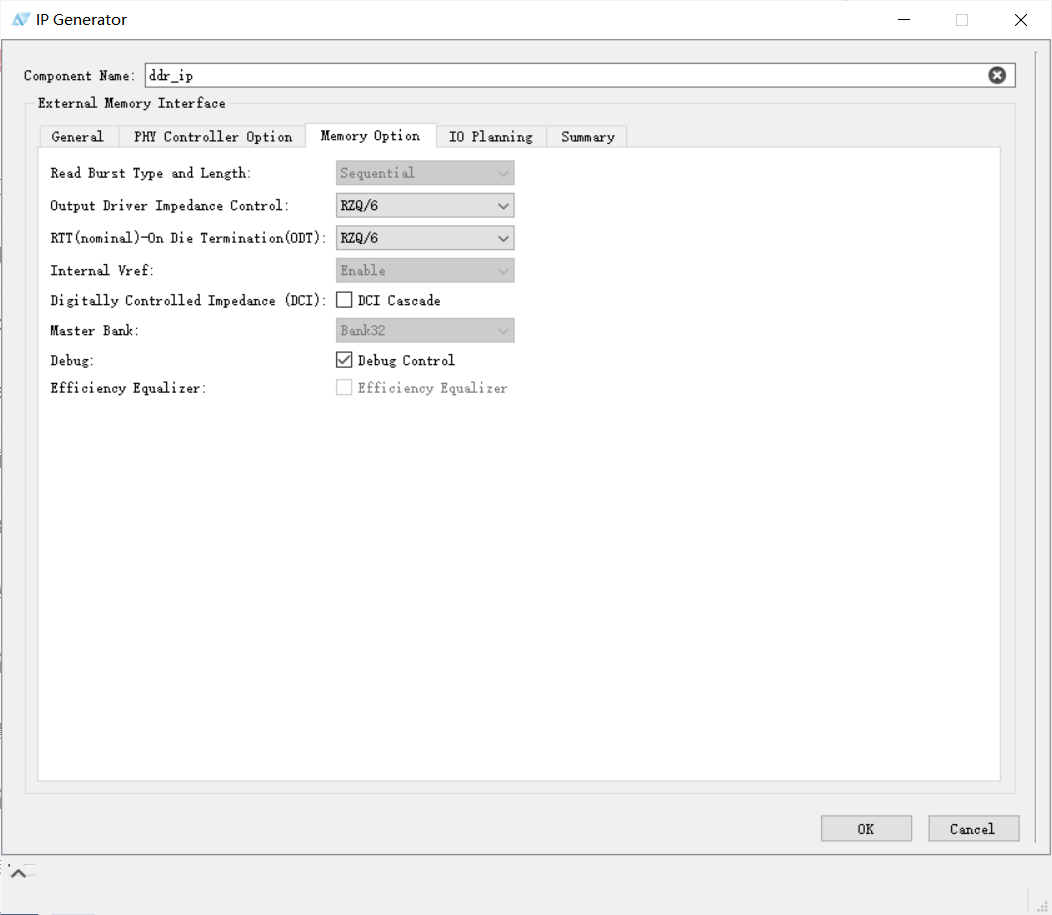

选择与板卡设计的阻抗一致的ODT,并勾选串口调试Debug Control

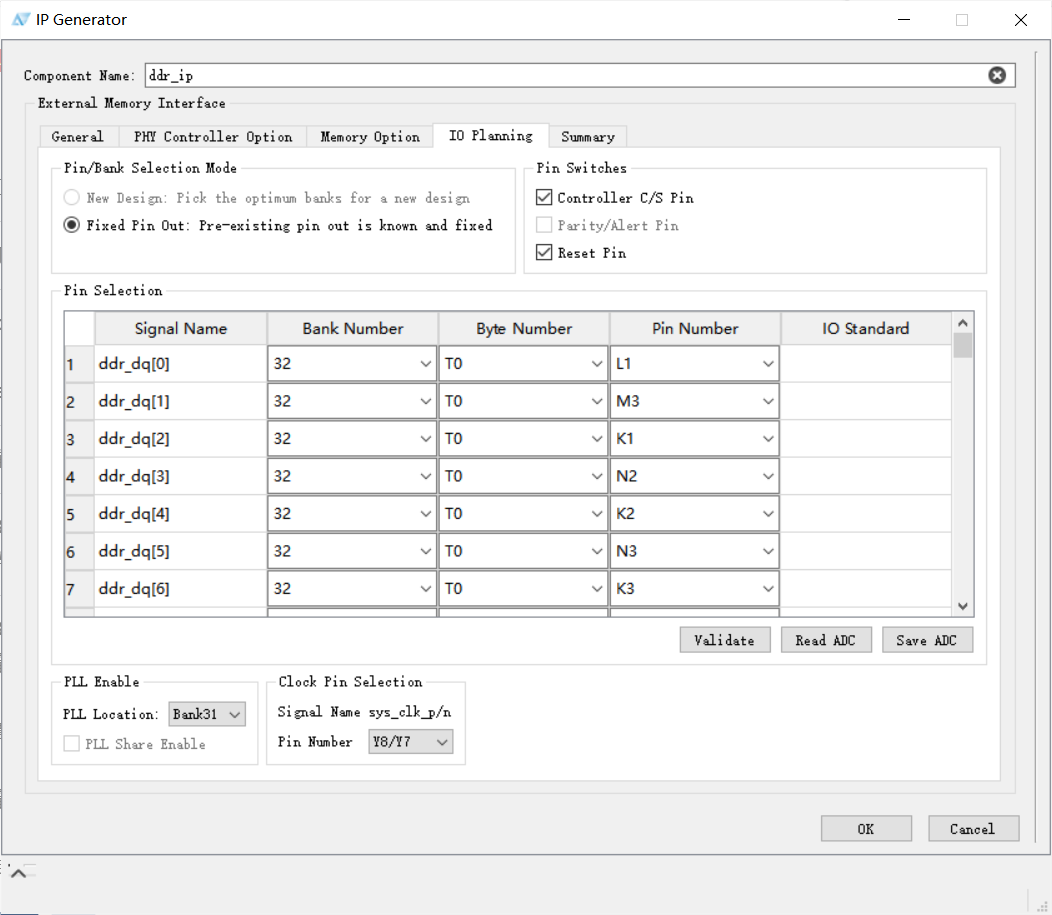

导入管脚信息以及时钟信息,点击验证管脚并生成ip,可以使用工程目录下的ddr_ip.adc文件导入管脚配置。

例化最简DDR模块,仅包含时钟和串口输出。

module top(

input clk,

output uart_tx

);

ddr_ip (

.sys_clk_p (clk),

.sys_rstn (1'b1),

.uart_txd (uart_tx)

);

endmodule

添加管脚约束。

set_pin_assignment { clk } { LOCATION = Y8; IOSTANDARD = LVDS18; }

set_pin_assignment { uart_tx } { LOCATION = R22 ; IOSTANDARD = LVCMOS33; }

编译完成后,即可连接串口查看打印数据,使用波特率115200,无校验位,设置“字符”接收模式再接上串口,如果显示“HandOff to DFI”表示DDR通路测试正常。

PH1A 工程说明

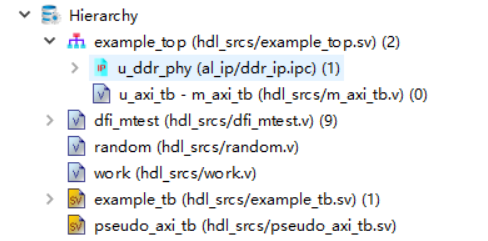

工程结构如下

example_top是工程顶层文件。

ddr_phy是DDR IP,其中包括axi和native两种接口。

m_axi_tb为axi的激励文件。

example_tb为native接口激励文件。

dfi_mtest为dfi接口激励文件。

pseudo_axi_tb为axi总线的测试激励。

prbs、random、work为data_source的压力测试数据源。

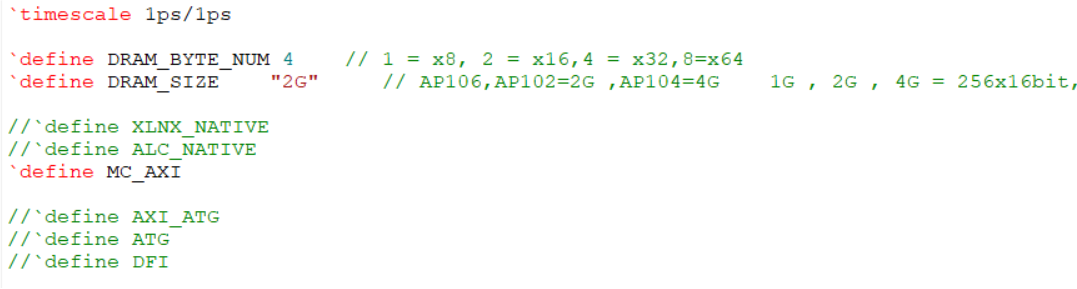

当前的工程配置是将DDR IP配置为 axi 接口,使用 axi_tb 测试 DDR 读写是否正确。在顶层文件example_top 中,可以通过宏定义修改接口。定义中的“DRAM_BYTE_NUM”为2,表示DDR的位宽为x16,改为4表示x32。DRAM_SIZE表示使用的颗粒容量。IP中的位宽修改在PHY Controller Option选项卡中的Data Width。

上板测试时,观察LED状态。工程路径下best_result文件自带bit文件,可以下载demo板测试。

led7:DDR读写全部正常,灯间隔1s左右闪烁一次。

led8:表示valid信号,即mc/axi的数据正在读有效,灯亮为正常(比其它灯暗一点)。

Led9:表示error信号,灯灭表示无数据出错。

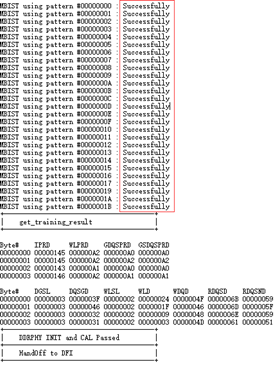

通过串口连接到PC,打印如图所示,pattern都为Successfully信息表示正常。

关于工程的仿真,以及DDR demo的其它详细信息,参考工程附带的DDR测试说明文档。

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1