注意:该工程需要在 6.0 及以上版本 TD 中打开,不支持老版本 TD

1. 工程说明

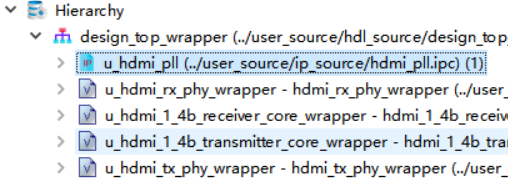

该demo是一个720p HDMI示例,工程结构如下图所示:

顶层信号说明如下:

I_sys_clk:系统时钟信号输入。

I_rst_n:系统复位信号,低电平有效。

I_hdmi_rx_clk_p、I_hdmi_rx_ch0_p、I_hdmi_rx_ch1_p、I_hdmi_rx_ch2_p:接收 HDMI 的差分时钟和三个数据通道。

O_hdmi_tx_clk_p、O_hdmi_tx_ch0_p、O_hdmi_tx_ch1_p、O_hdmi_tx_ch2_p:输出 HDMI 的差分时钟和三个数据通道。

I_hdmi_rx_ddc_scl、IO_hdmi_rx_ddc_sda:接收 HDMI 的 DDC(Display Data Channel)信号,用于 EDID(Extended Display Identification Data)的通信。

O_hdmi_tx_ddc_scl、IO_hdmi_tx_ddc_sda:发送端的 DDC 信号。

整体数据流为:

HDMI 输入物理层(hdmi_rx_phy_wrapper)--> HDMI 接收模块(hdmi_1_4b_receiver_core_wrapper)--> HDMI 发送模块(hdmi_1_4b_transmitter_core_wrapper)--> HDMI 输出物理层(hdmi_tx_phy_wrapper)

pll模块用于生成 2.5 倍 pclk 和 5 倍 pclk,对于 720p 60hz,像素时钟 pclk 的频率为 74.25。

接收模块可以将输入的 HDMI 信号解码成原生同步信号和数据或axi流数据。

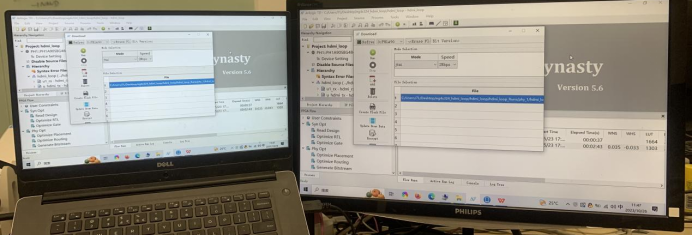

2. 上板测试

烧录 bit 文件后,连接 PC 与 HDMI_IN, 显示器与 HDMI_OUT,调整输出分辨率为 720P,图像正常输出至显示器,实验成功。若发生花屏问题,需检查分辨率设置是否正确。

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1