本实验通过VTC模块产生的视频时序和若干种测试图形,并利用FPGA内部资源实现HDMI协议,通过HDMI输出接口输出1080P@60fps的视频图像以进行HDMI_OUT的测试。

1.系统框图

2.HDMI_IP介绍

HDMI(High Definition Multimedia Interface) 是一种全数字化影像和声音发送接口,可以发送未压缩的音频及视频信号。

本HDMI Transmitter设计支持的功能如下:

➢ 最高支持 1080p60 显示分辨率。

➢ 支持两路音频输入。

➢ 支持 RGB444 和 YUV444 。

➢ 支持内部视频测试源。

➢ 支持 EDID 读取。

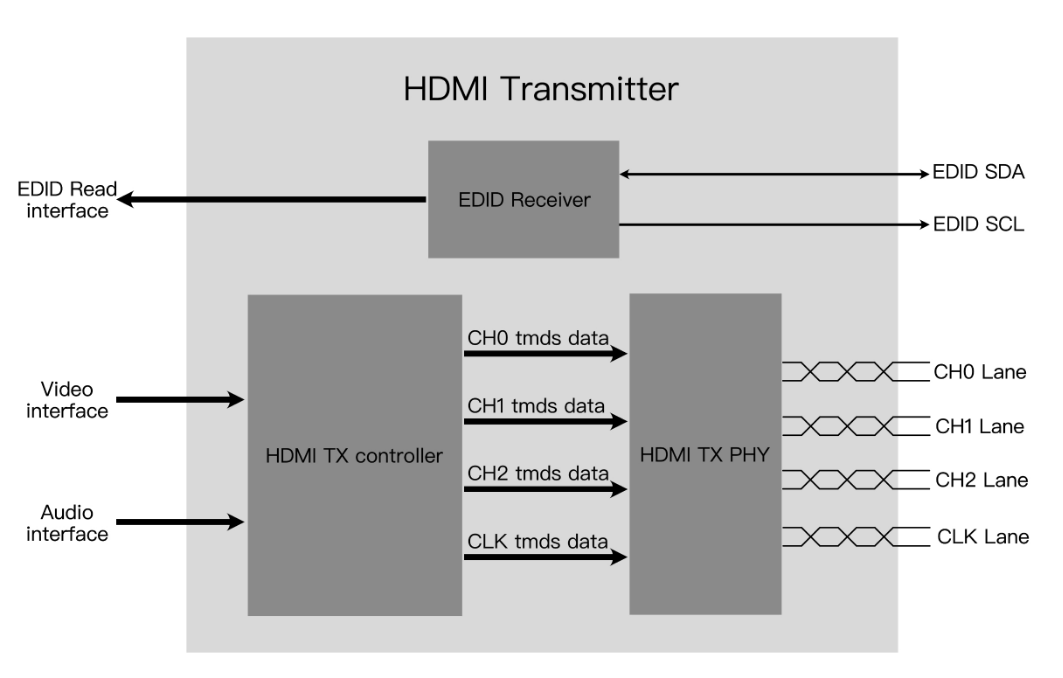

2.1 HDMI_IP系统框图

HDMI Transmitter设计包含以下三部分:

HDMI_TX_controller:HDMI的协议层,用于将音频数据、视频数据以及配置数据打包编码,输出 TMDS 编码数据。

HDMI_TX_PHY:HDMI的物理层,用于将协议层传输的 TMDS 编码数据转换为串行数据并发送出去 。

EDID_Receiver:读取 HDMI 接收端的 EDID 数据。

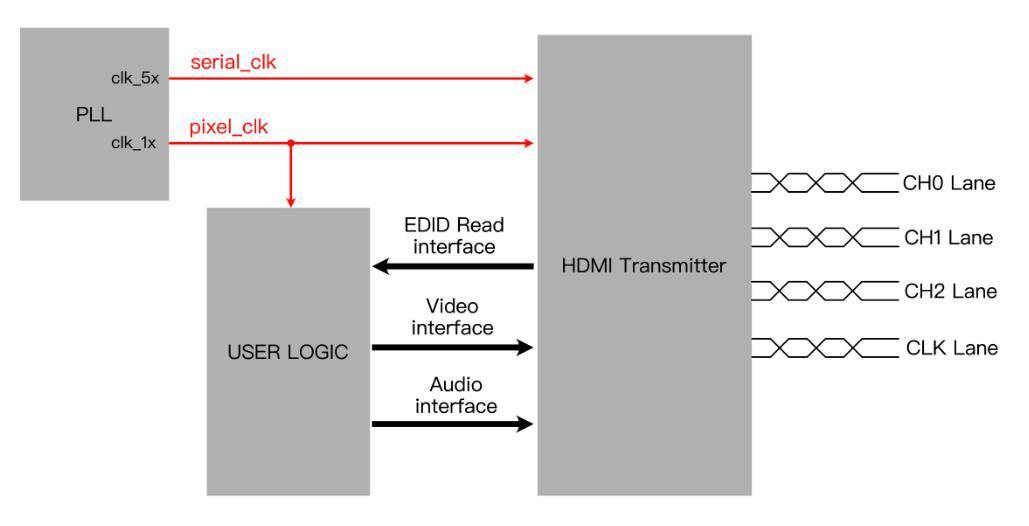

2.2 HDMI IP时钟架构

HDMI Transmitter工作需要两个时钟,像素时钟 pixel_clk和串行发送时钟 serial_clk。两个时钟都是通过 PLL生成,其中 serial_clk的频率是 pixel_clk频率的五倍。

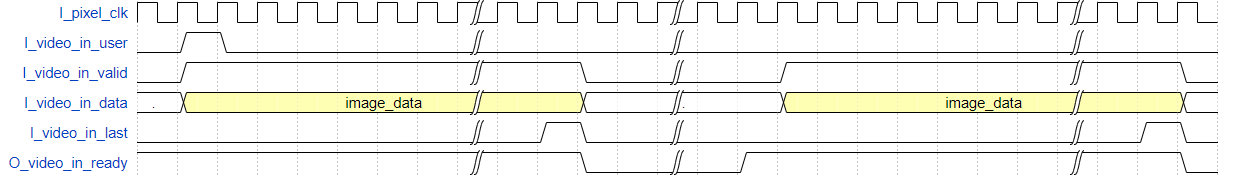

2.3 HDMI IP视频接口时序

视频接口时序图如下图所示:

I_video_in_ user 信号是帧起始信号,为一个单时钟周期信号,在第一行第一个有效数据拉高。I_video_in_valid 是数据有效信号, I _video_in_last 是行结束信号,在一行数据的结尾拉高。 O_video_in_ready是接收端准备信号,为高表示可以写入数据,在 I _video_in_last 为高之后会拉低。

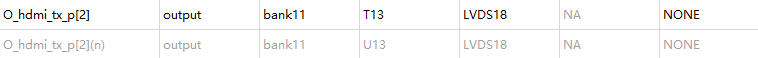

3.引脚配置

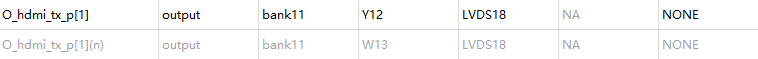

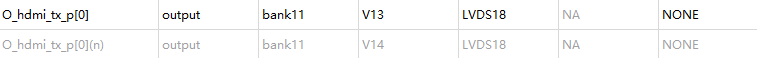

IO引脚配置如下图所示:

系统时钟为N18:

HDMI_CLK_P为V17,N为W17:

HDMI_TX_P[2]为T13,HDMI_TX_N[2]为U13:

HDMI_TX_P[1]为Y12,HDMI_TX_N[1]为W13:

HDMI_TX_P[0]为V13,HDMI_TX_N[0]为V14:

4.烧录bit文件

将./fpga_prj_Runs/phy_1下的bit流文件烧录到开发板中。

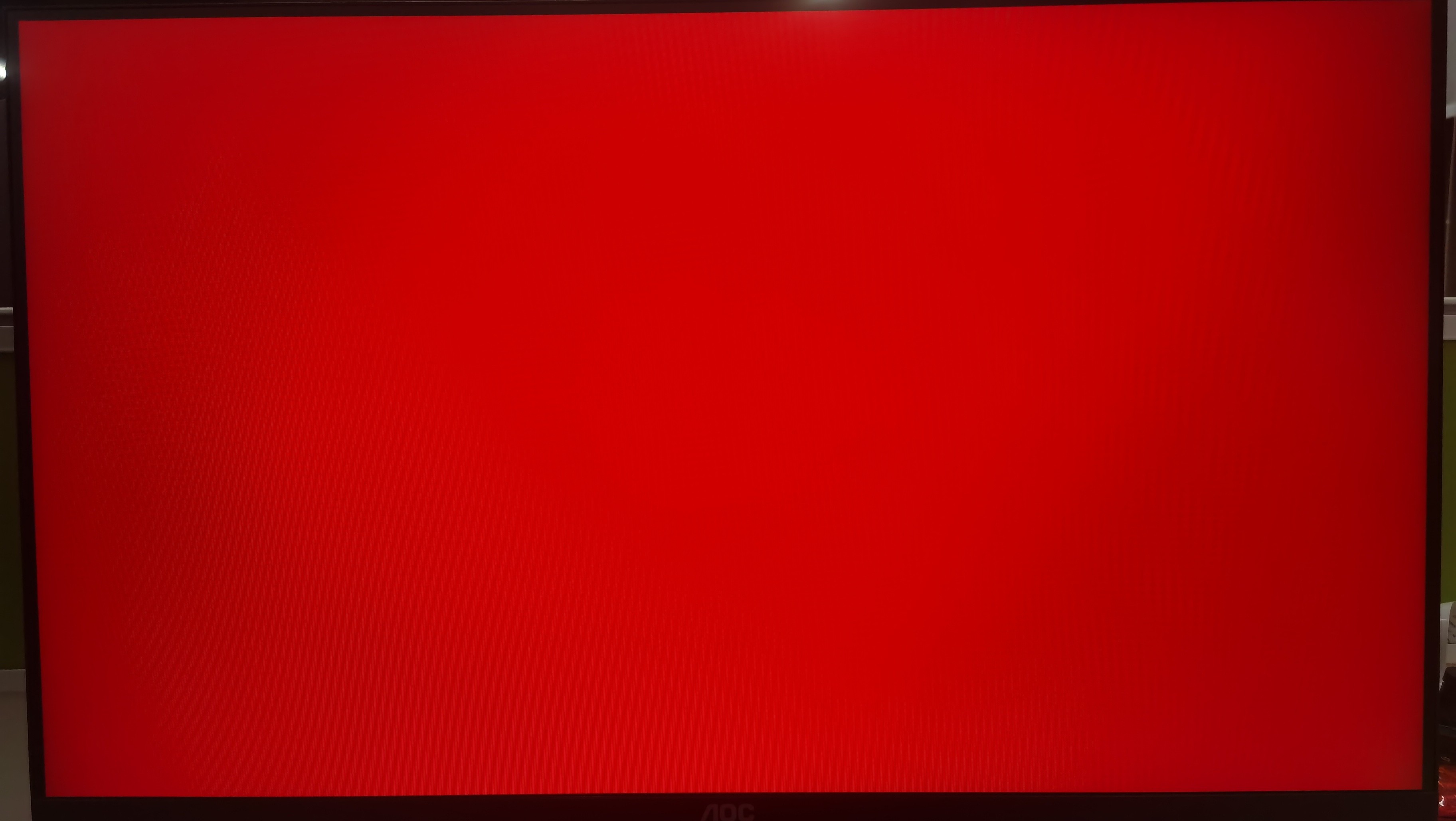

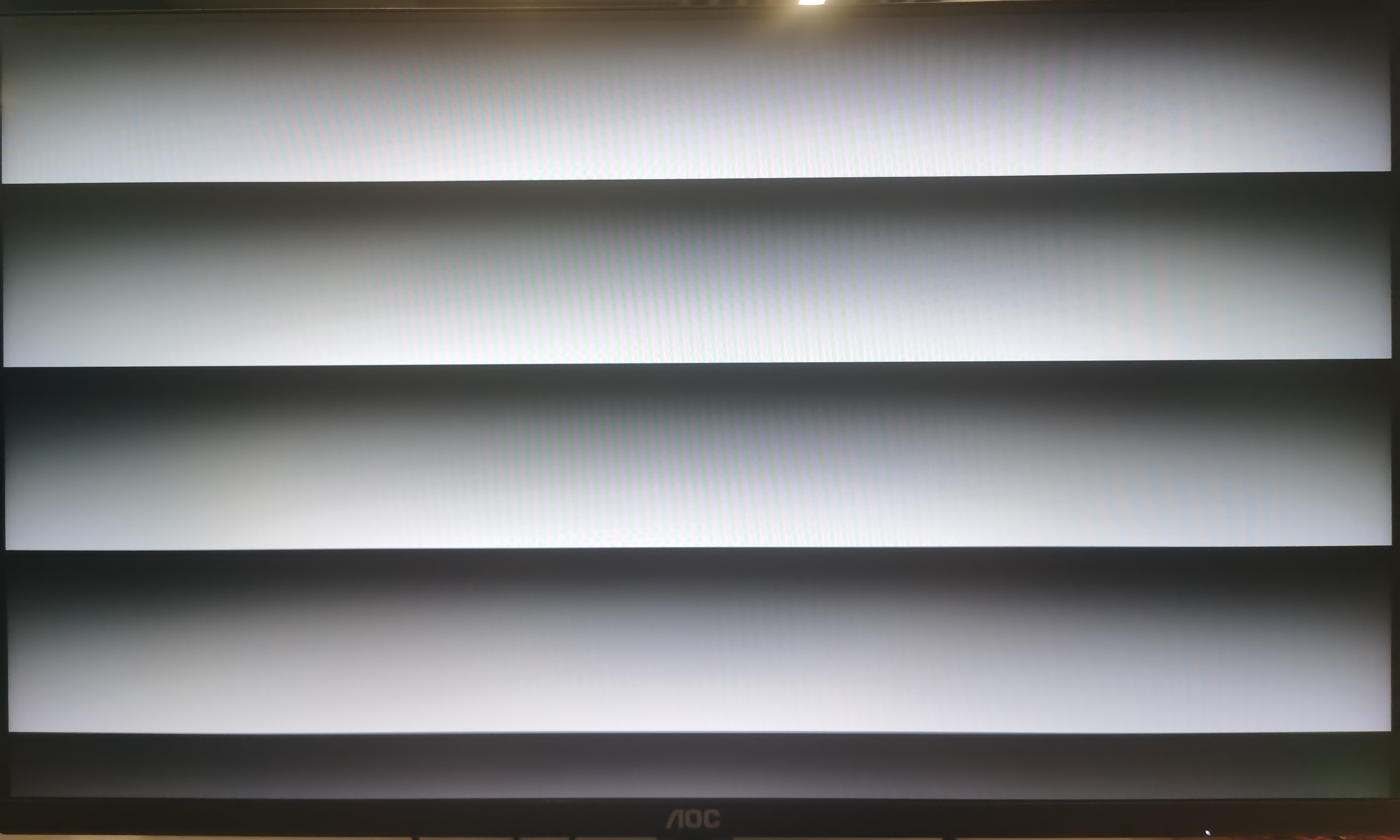

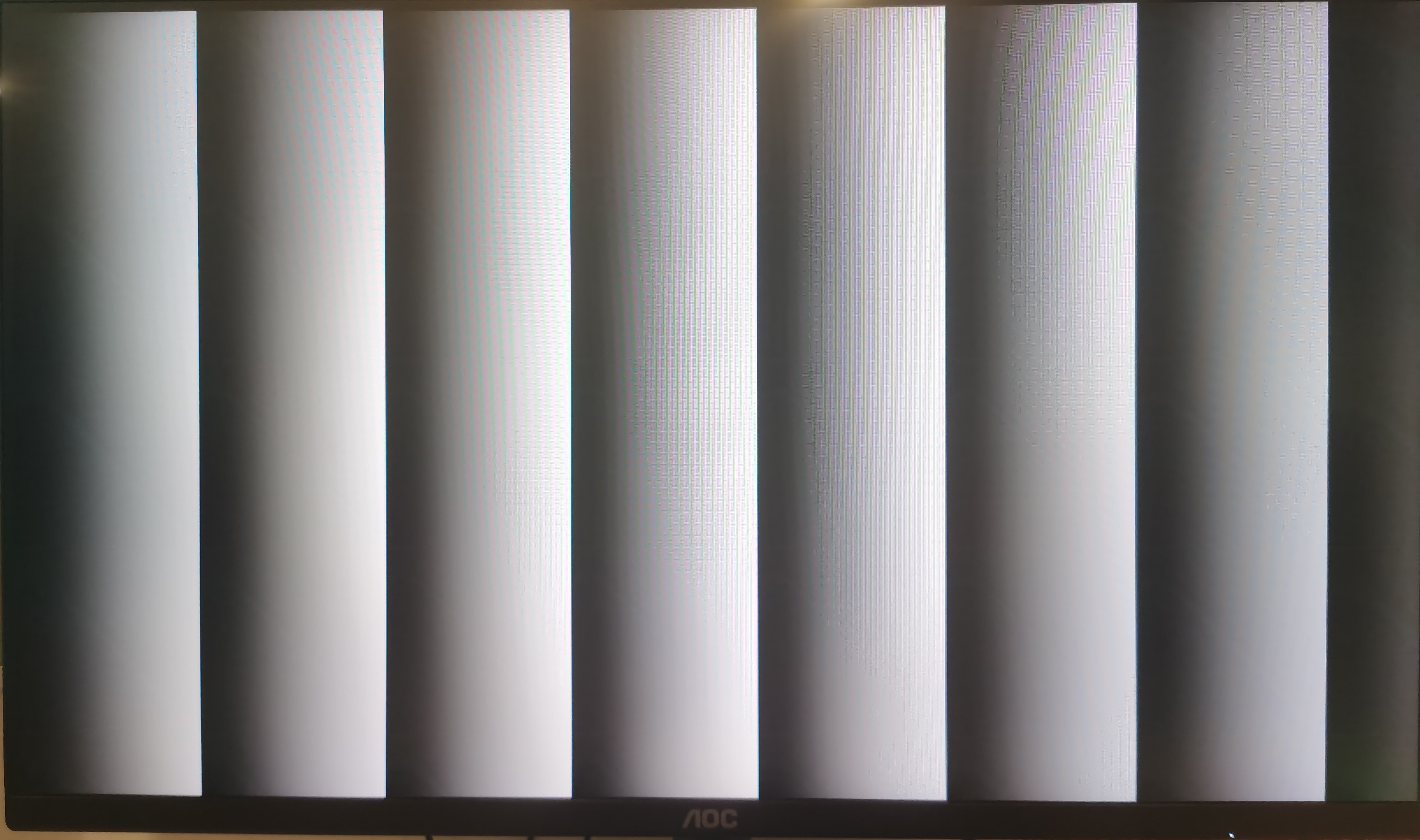

5.实验结果

屏幕上依次显示黑屏,白屏,红屏,绿屏,蓝屏,白黑渐变,红黑渐变,绿黑渐变,蓝黑渐变,彩条等,循环演示:

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1