Anlogic AD 7266子板功能测试

本实验任务使用FPGA驱动AD7266模块实现模拟数据的采集和转换,测试中使用信号发生器向ADC分别发送正弦波信号,高电平和低电平信号,验证ADC芯片是否功能正常。

1.AD 7266芯片介绍

AD7266芯片集成有两个独立的高速12位逐次逼近A/D转换单元、吞吐量为2Msps、低功耗,单电源工作2.7~5.25V。在每个D/A前有三复用开关可组成三路差分或六路单端信号输入;采样保持放大器为带宽10MHz的低噪声电路。

2.硬件电路设计

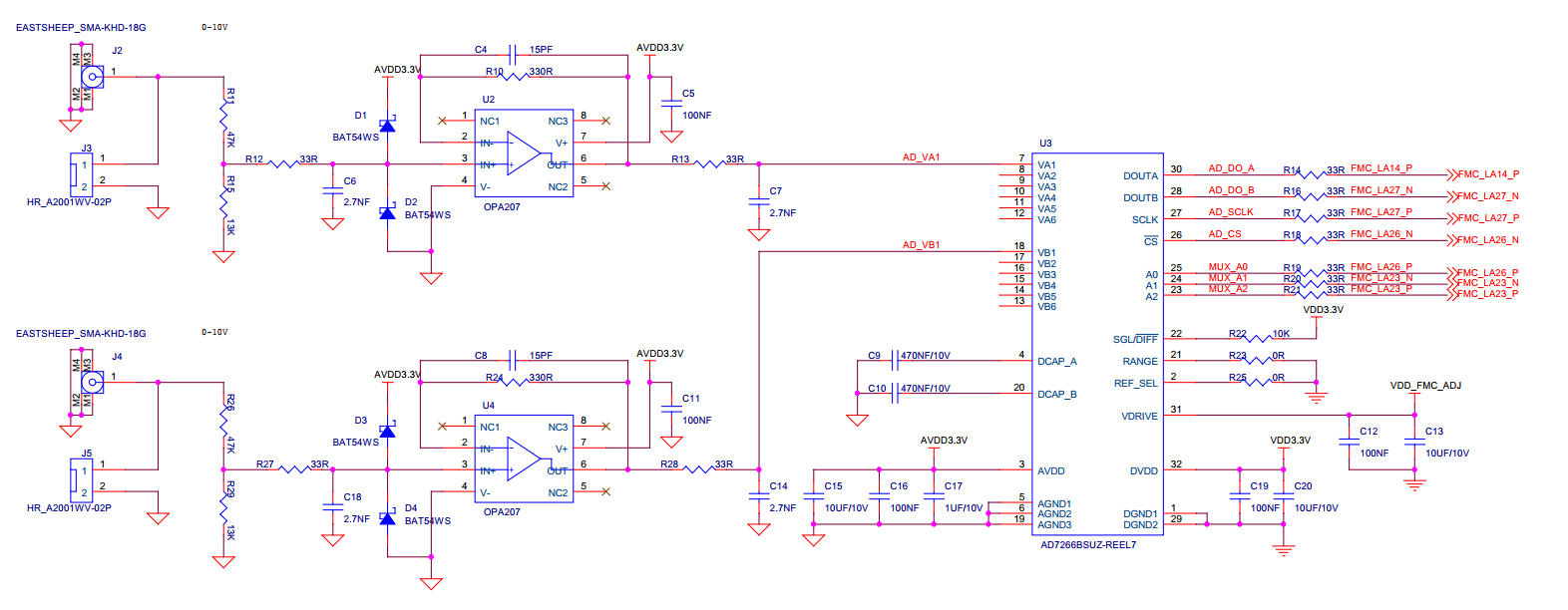

以下为VeriMake FMC ADC 扩展模块原理图。

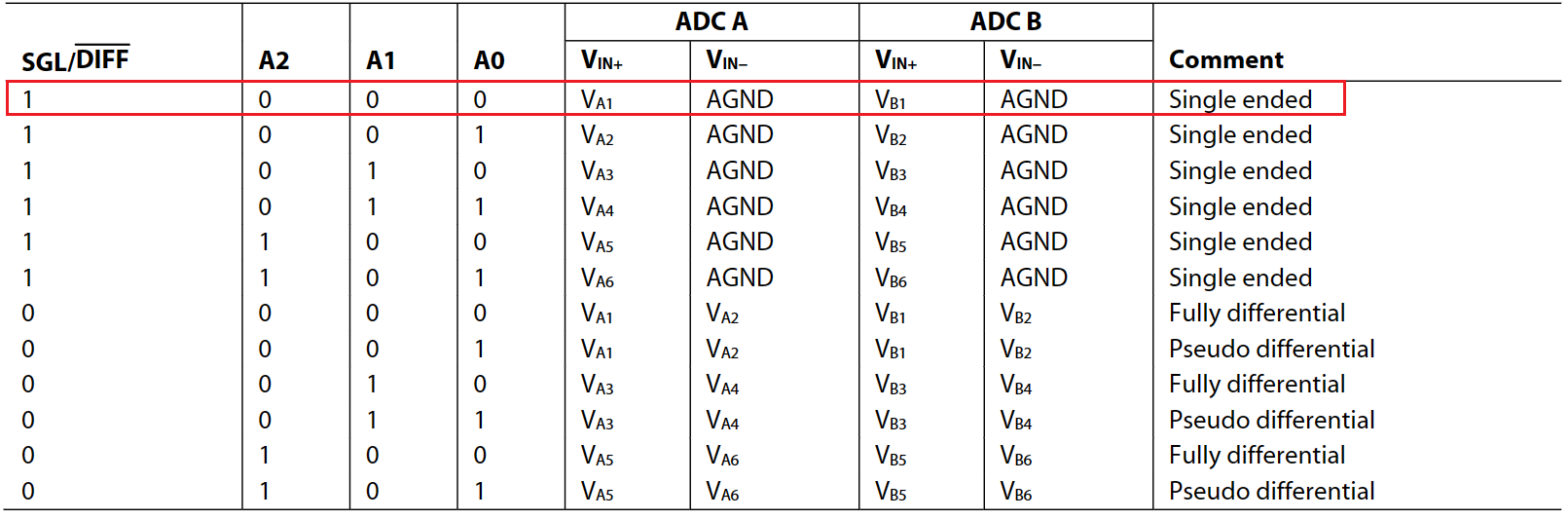

下表AD7266芯片模拟输出类型和通道选择表。

根据硬件设计图和AD7266芯片手册可以发现,模拟输入模式为单端模式,仅使用了VA1和VA2通道,故驱动代码设计中应设置A2A1A0值为000。

模拟输入范围选择:RANGE 引脚,该引脚连接至逻辑低电平,模拟输入范围为 0 V 至 VREF,即010V。

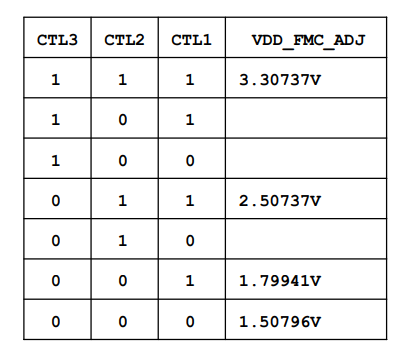

硬件设计中设计Vdriver引脚由VDD_FMC_ADJ控制,根据下图配置电压为3.3v。

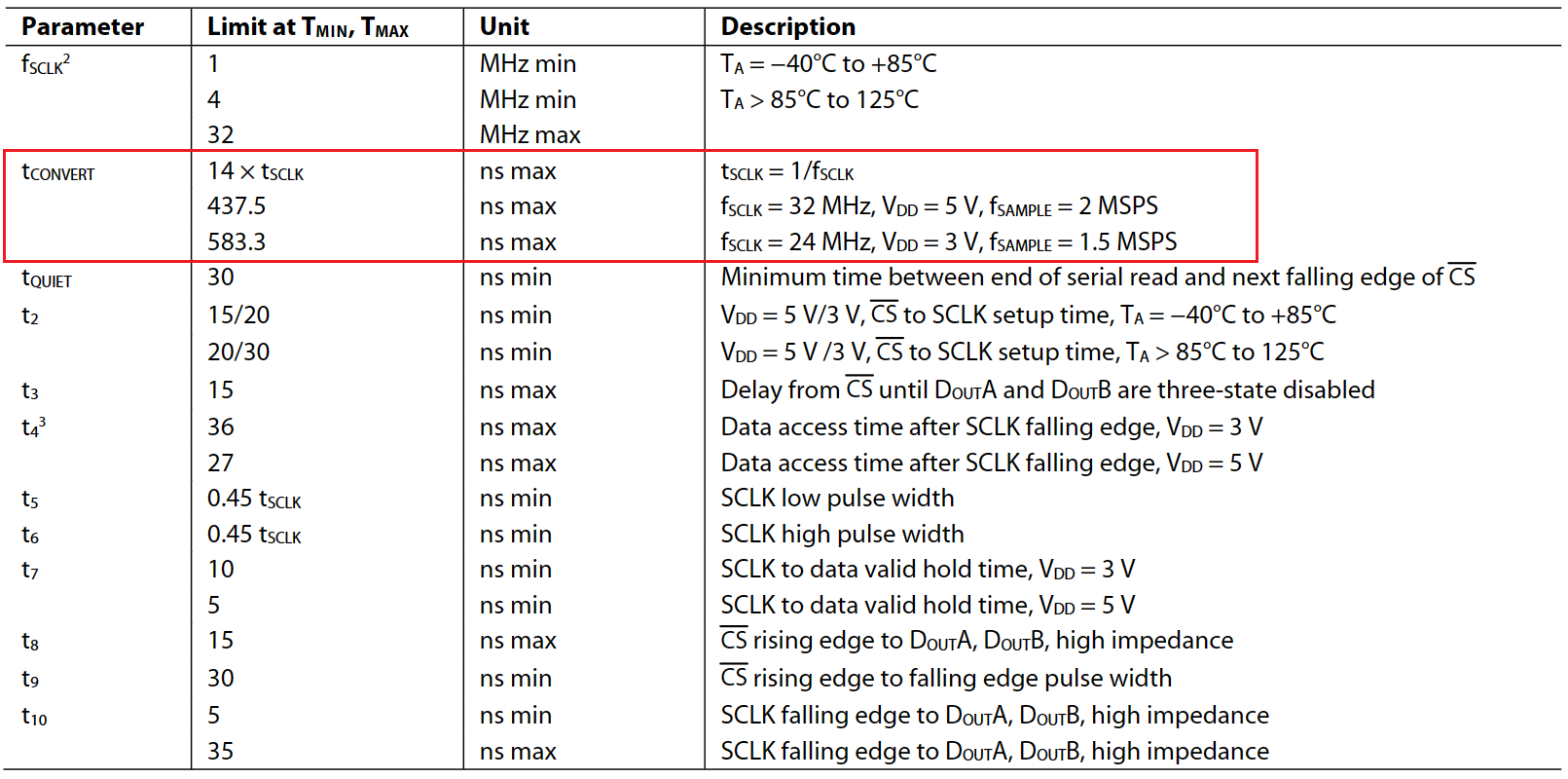

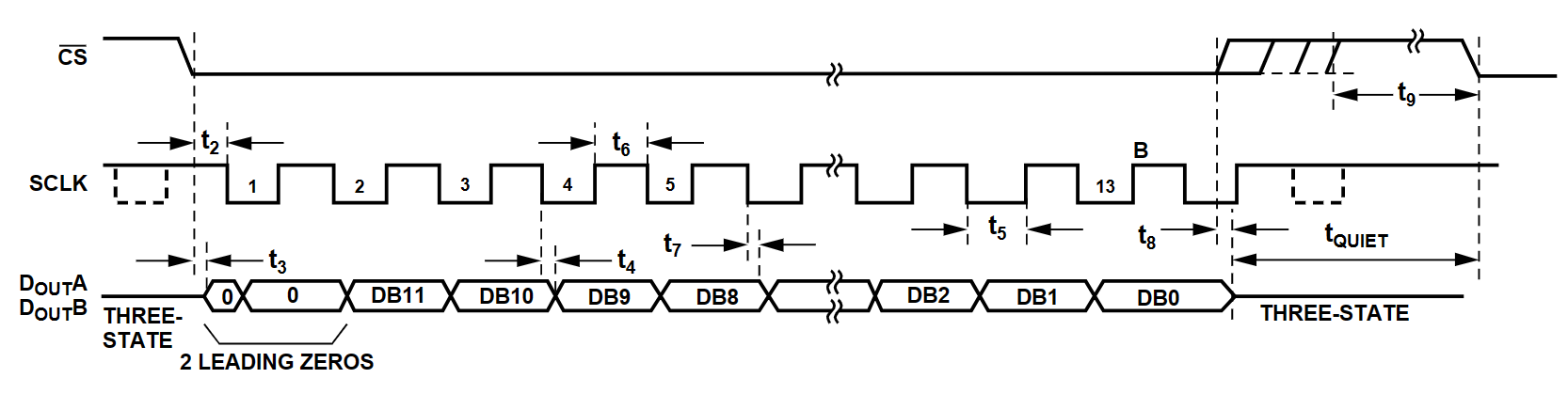

AD7266时序要求,最大转换时间TCONVERT为14×TSCLK。

精确控制CS*与SCLK的时序,从串行数字接口获得转换后的数据,下图为串行接口时序图。

3.系统框图

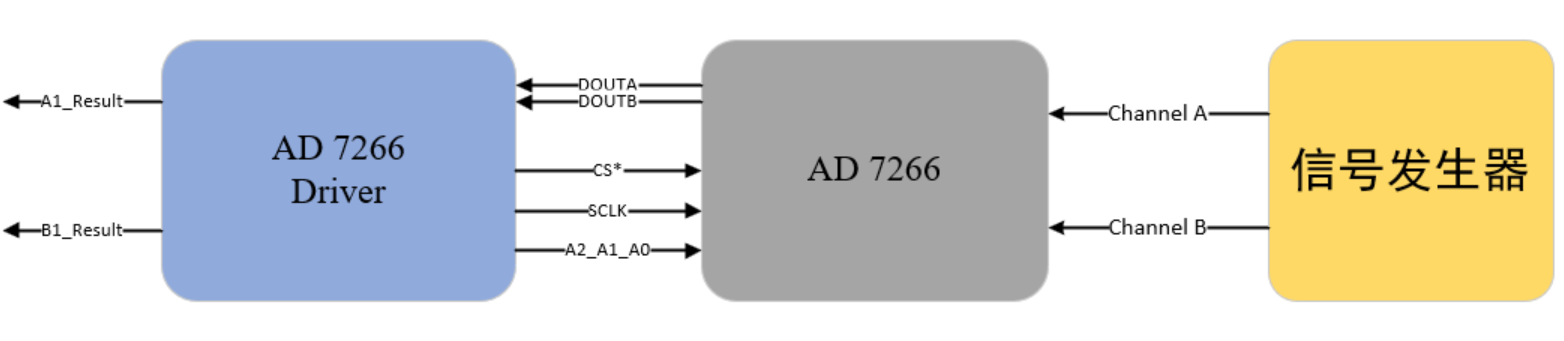

系统框图如图所示,FPGA驱动AD7266模块从信号发生器采集模拟信号,并将AD7266输出DOUTA和DOUTB解码,转换为A1_Result和B1_Result,结果通过安路IDE自带的CWC工具抓取结果信号观察。

4.上板验证

4.1硬件连接

首先进行硬件接线,将FPGA开发板于FMC ADC子板以及信号发生器连接,如图所示。

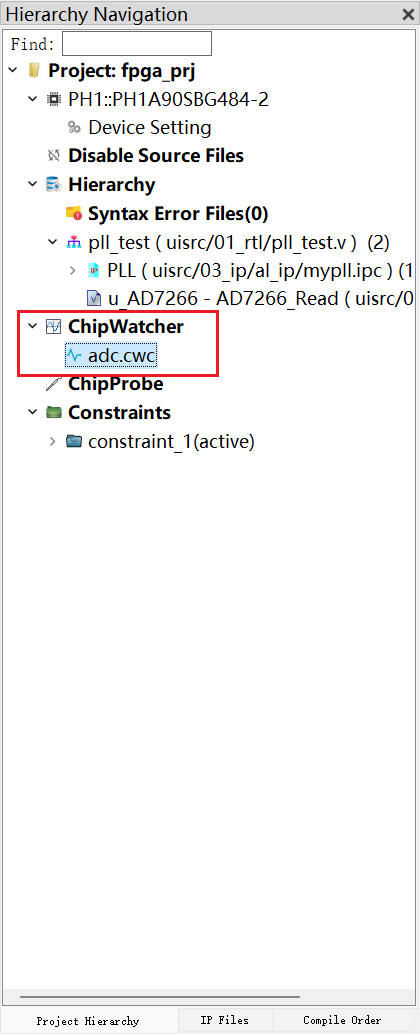

4.2下载bit流文件,并打开CWC文件

确保连线正常后,打开工程文件,将工程目录\fpga_prj\fpga_prj_Runs\phy_1下的fpga_prj.bit下载至开发板。之后打开工程目录中adc.cwc

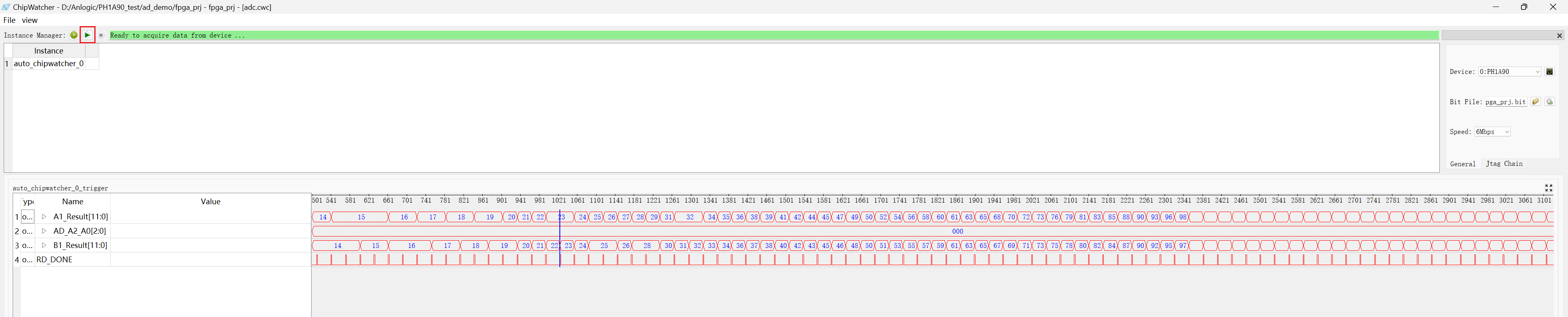

进入ChipWatcher后, 点击持续触发按钮即可观察数据。

4.3实验结果

采样电压 V = ( Result /4096 ) *10 V 。

该实验中通道A与通道B采集同一信号源,故结果应保持一致。

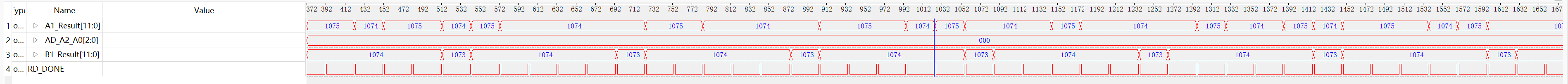

输入信号为高电平( 3V )时,结果如图所示:

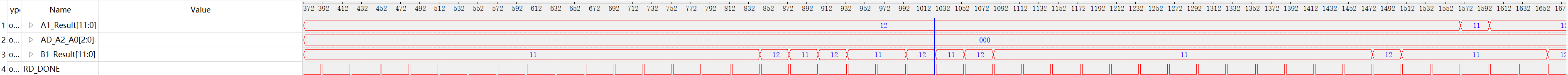

输入信号为低电平( 0V )时,结果如图所示:

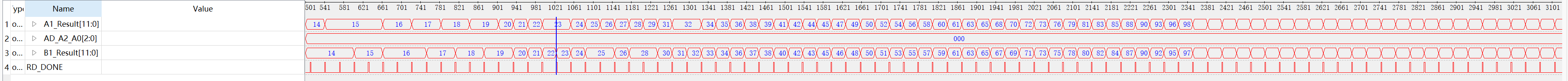

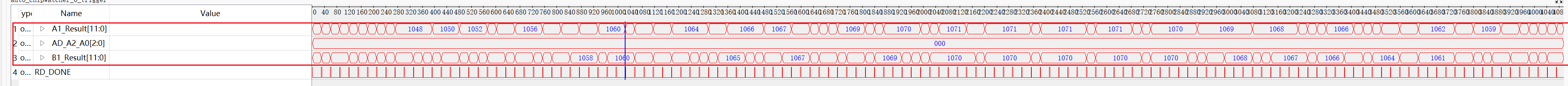

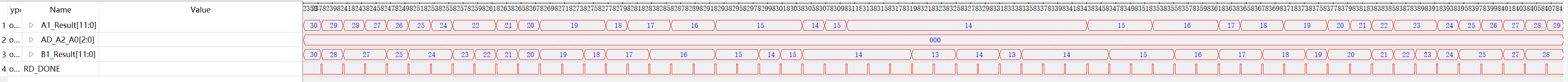

输入信号为正弦波信号时,结果如图所示:

数据逐渐从零开始递加。

数据递加至峰值( 设置的Vdd为3v,对应数值约为 4096*3V / 10V = 1228 )后,开始递减。

数据逐渐递减,并递减至零后又开始递增。与正弦波信号变化一致, 验证成功。

注意:该模块支持采样电压范围为0 ~ 10V

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1