往往某家的 FPGA 产品都会使用独家的开发环境和仿真器,例如 Xilinx 有 ISE,Altera 有 Quartus II,或者也可以使用专业 EDA 厂家的仿真器如 Modelsim。但是 Modelsim 在停止维护之后,使用起来并不友好,所以也会推荐一些其他仿真平台。

开发平台 :

巧妇难为无米之炊,在开发软件国产化浪潮下,本系列也采用安路科技的 Tang Density 软件作为开发平台、SparkRoad 作为开发板,具体的下载操作和教程可见 Verimake 论坛链接:资料汇总索引 - VeriMake 和安路FPGA竞赛用开发板SparkRoad-V教程 - VeriMake

仿真平台 :

现有的仿真平台有很多,例如 Modelsim、Icarus Verilog、Quartus、Vivado、Questa 等。因为 Modelsim 停止维护后,在仿真的过程中会出现很多不友好的问题,所以将一一介绍一些其他的仿真平台以供替代。

Icarus Verilog&VS code:

相较于其他几种软件的复杂和工程完整程度,如果只是为了基本地验证代码的正确性和简单地仿真,Icarus Verilog 这样一个轻量级软件也可以胜任。

首先安装 VS code 软件,此过程在网上有很多教程,并且有许多插件教程以供挑选,对于此仿真过程,需要安装 Verilog-HDL/SystemVerilog/Bluespec SystemVerilog 插件:

此插件并不需要增加环境变量,直接启用即可。(有一些 verilog 相关插件需要设置环境变量的,会在后面一步步更新)

Icarus Verilog 是一个轻量、免费、开源的 Verilog 编译器,基于 C++实现,开发者是 Stephen Williams ,遵循 GNU GPL license 许可证,安装文件中已经包含 GTKWave 支持 Verilog/VHDL 文件的编译和仿真,命令行操作方式,类似 gcc 编译器,通过 testbench 文件可以生成对应的仿真波形数据文件,通过自带的 GTKWave 可以查看仿真波形图,支持将 Verilog 转换为 VHDL 文件。

Iverilog 安装时,默认会把 GTKWave 一起安装,用于查看生成的波形图。

Iverilog 支持 Windows、Linux 和 MacOS 三大主流平台,截止 2019 年 12 月 1 日,最新版本 v 11-20190809下载:

http://bleyer.org/icarus/iverilog-v11-20190809-x64_setup.exe

当与 VS code 联合使用时,步骤如下:

在. V 文件所在的文件所在文件夹同时新建 testbench 文件,例子如下:

并且在 testbench 文件中添加引入源文件代码 `include"xxxx.v" ,注意最后没有;。

与一般的 tb 文件写法稍有不同,需要再代码中添加语句。

在 initial 模块中需要添加

$dumpfile("tb_sram1_read_ctrl.vcd"); //对应存入的文件名,波形图

$dumpvars(0, tb_sram1_read_ctrl); //对应module名字

$finish;

这三行代码,具体位置如下显示:

initial begin

$dumpfile("tb_sram1_read_ctrl.vcd"); //对应存入的文件名,波形图

$dumpvars(0, tb_sram1_read_ctrl); //对应module名字

SYSCLK = 1'b0;

NSYSRESET = 1'b0;

parameter1 = 16'd10;

parameter2 = 16'd4;

read_and_process_flag = 1'b0;

#20000 read_and_process_flag = 1'b1;

#20 read_and_process_flag = 1'b0;

#1000000 read_and_process_flag = 1'b1;

#20 read_and_process_flag = 1'b0;

$finish;

end

其余代码位置并不需要改动。

如果希望在 VS code 的终端按位输出数值,可以类比 C 语言,在 tb 文件中增加一个 initial 模块,如下:

initial begin

$monitor("t = %3d, SrcA = %b, SrcB = %b, ALUControl = %b, ALUResult = %b, Zero = %b \n", $time, SrcA, SrcB, ALUControl,ALUResult, Zero);

end

虽然说对于多个输出的程序来说在终端显示远没有通过波形图观察来的方便,每太啥必要。

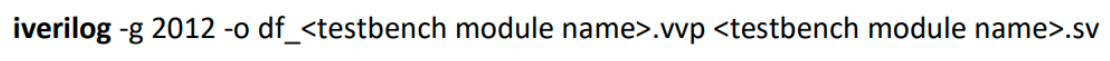

在“终端”中新建终端,并在终端中依次输入以下三个命令:

第一行代码,需要将 df_<testbench module name> 整体改写为 tb 文件的 module 的名称,同时因为查找到的手册是基于 System Verilog,所以第一行代码最后是. Sv,如果是基于 Verilog 代码,则第一行代码最后改为. V,实现了基于. V 文件的 tb 文件的生成。

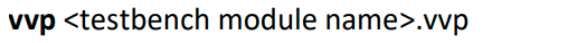

第二行代码,实现了生成相应的波形文件。

第三行代码,打开生成的波形文件。

如果代码无误,运行成功且不报错。

上述三行代码运行无误后,自动会弹出 GTKWave 软件页面:

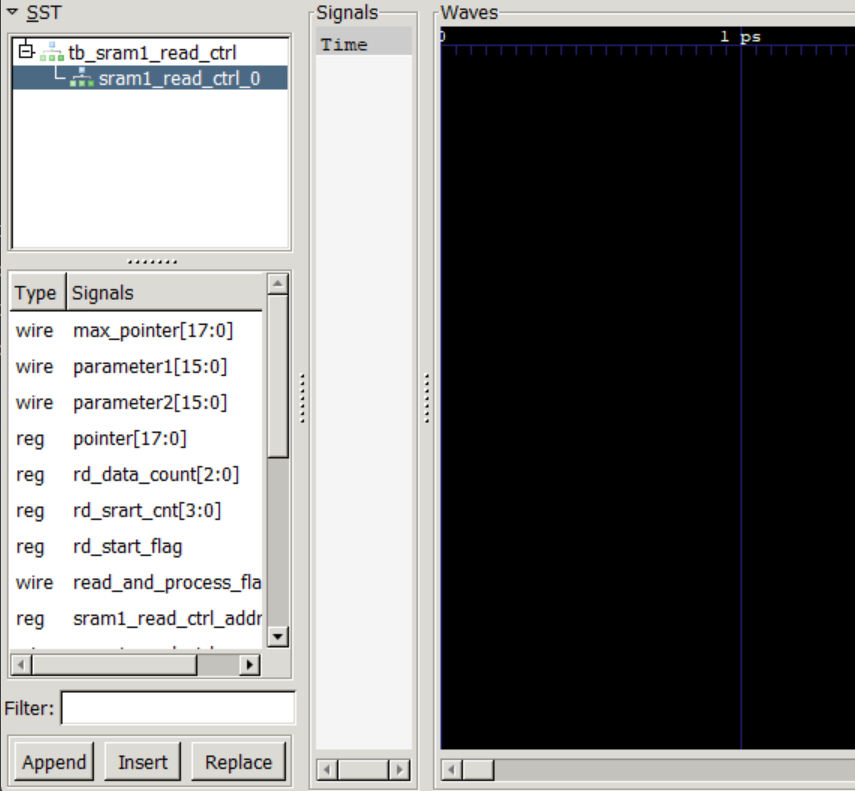

点击 File,选择 Open New Tab,在弹出的页面选择刚刚生成的. Vcd 文件。在 SST 窗口点击文件前的+号,显示界面如下:

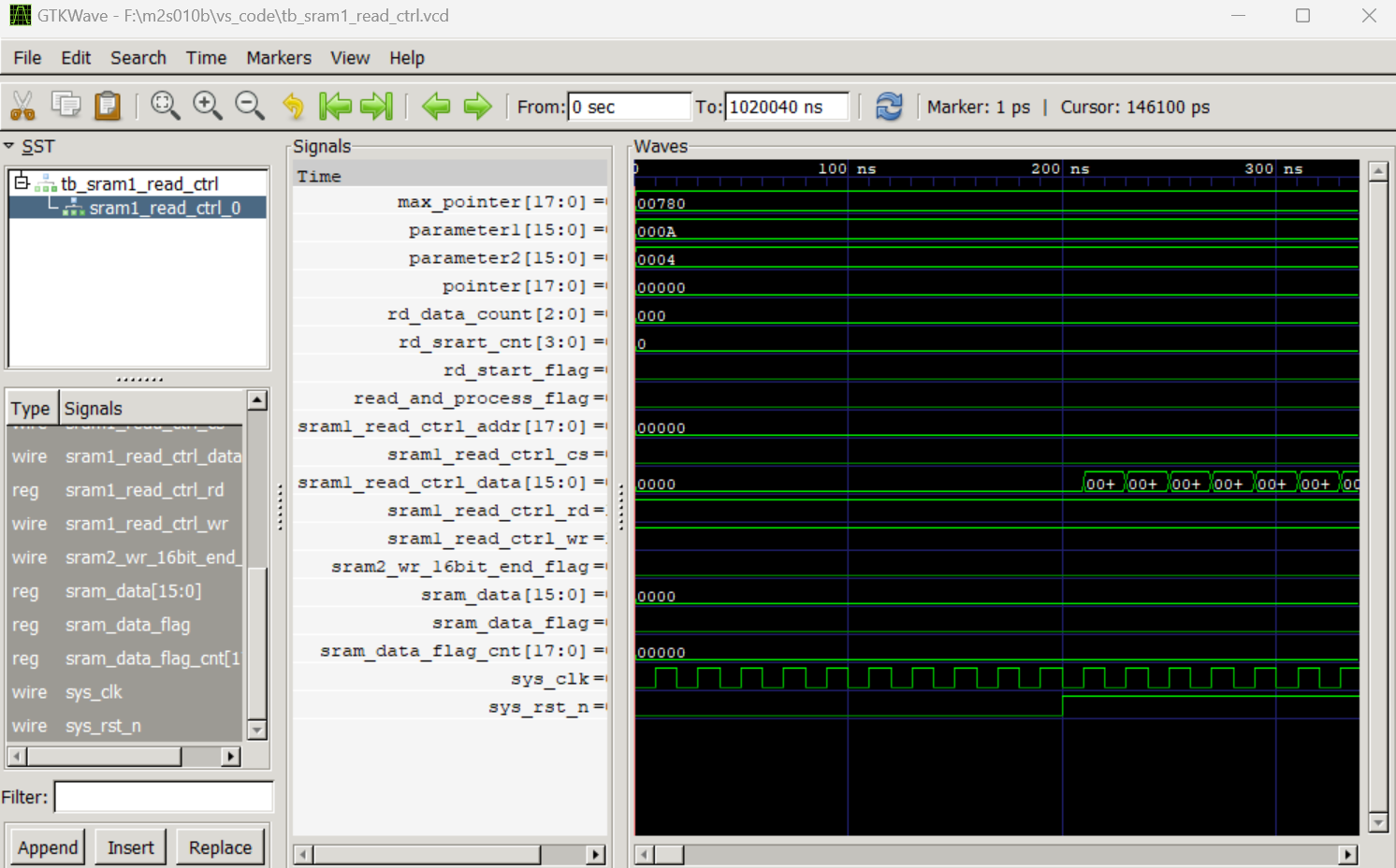

选择所有信号(可以先点击第一个信号,再按住 Shift,再点击最后一个信号,则完成全选),点击左下角 Append,在右侧显示相应波形图文件,如下:

则流程完成。

案例展示:

实现 100 分频器:

Verilog 代码如下:

module ceshi

(

input clk,

input rst,

output sck_reg

);

reg sck_reg;

reg [8:0]delay_count;

always@(posedge clk)

begin

if(~rst)

delay_count<=0;

else if(delay_count==99)

delay_count<=0;

else

delay_count=delay_count+1;

end

always@(posedge clk)

begin

if(~rst)

sck_reg<=0;

else if(delay_count<=50)

sck_reg<=0;

else if (delay_count>50) begin

sck_reg<=1;

end

end

endmodule

基于 VS code 和 Icarus Verilog 平台的 Testbench 代码如下:

`include "ceshi.v"

`timescale 1ns/1ps

module tb_ceshi;

reg clk;

reg rst;

reg [8:0]delay_count;

wire sck_reg;

initial

begin

$dumpfile("tb_ceshi.vcd");

$dumpvars(0,tb_ceshi);

rst=1'd0;

#20

clk=1'd0;

#20

delay_count=1'd0;

rst=1'd1;

#20000

$finish;

end

always @(*)

begin

forever begin

#10 clk=~clk;

end

end

ceshi ceshi_1(

.clk(clk),

.rst(rst),

.sck_reg(sck_reg)

);

endmodule

运行成功,不报错,新建终端,依次输入:

iverilog -g 2012 -o tb_ceshi.vvp tb_ceshi.v

vvp tb_ceshi.vvp

gtkwave

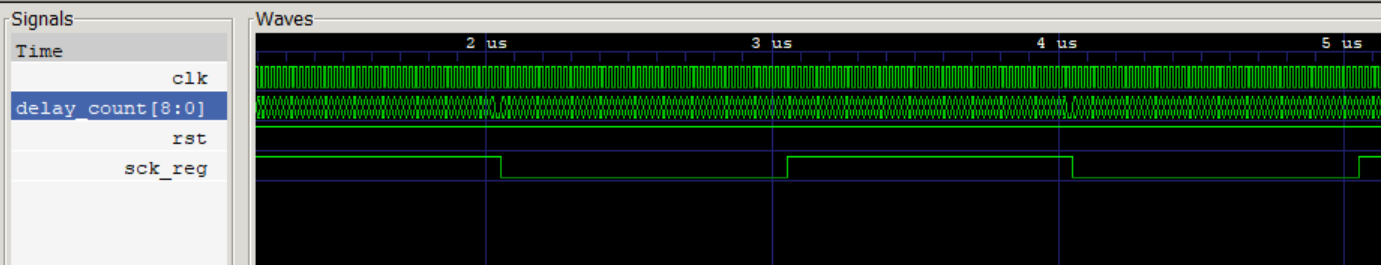

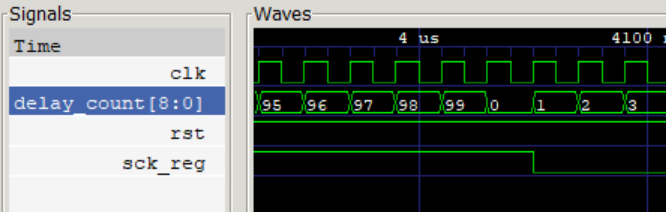

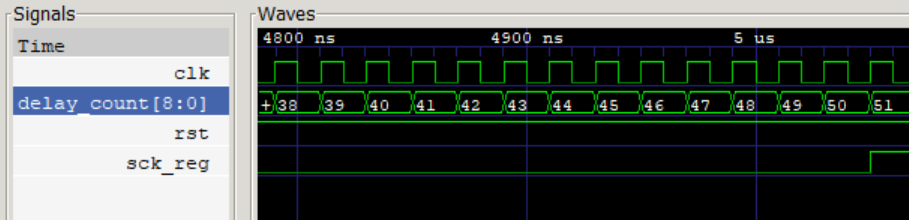

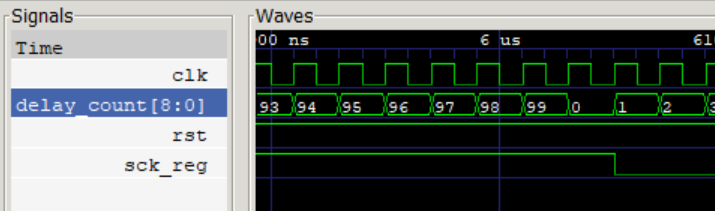

成功运行,仿真如下:

低电平由 delay_count=1 开始,delay_count=50 结束;

高电平由 delay_count=51 开始,delay_count=0(也可以理解为 100)结束,如下图所示:

反思与总结:分频器在许多场景都有广泛使用,又分为奇分频和偶分频,此处实现的是偶分频。且《搭建你的数字积木·数字电路与逻辑设计》(汤勇明版)P 163“SPI 控制器模块实例”中的代码针对分频器部分的代码,我认为是有问题的,仿真结果也不满足需求,有不同意见的欢迎讨论。下面附上汤代码:

module ceshi

(

input clk,

input rst,

output sck_reg

);

reg sck_reg;

reg [8:0]delay_count;

always@(posedge clk)

begin

if(~rst)

delay_count<=0;

else if(delay_count==49)

delay_count<=0;

else

delay_count=delay_count+1;

end

always@(posedge clk)

begin

if(~rst)

sck_reg<=0;

else if(delay_count==50)

sck_reg<=!sck_reg;

end

endmodule

Questasim:

对于 Questasim 软件,具体下载操作和教程可见:(34条消息) questasim的傻瓜式安装与仿真教程_树下等苹果的博客-CSDN博客

另外补充知识点:

几个按键的使用

Compile Out of date 按键常用于修改报错代码时,重新写的部分的单独编译。

对于这一行中的几个按键值得学习一下。

Restart 按键允许在修改之后再次生成波形图时,不必重新 simulation 和 add wave,直接使用即可。

Run Length 按键可以规定一次仿真的时长,过长或过短都不合适。

Run 按键每按一次,就允许再运行一次 Run Length 的时间长度。

Run Continue 按键允许一直运行下去。

Run-All 按键实现从编译到仿真的全部重新运行。

相关文件参考

(更多体操作会抓紧结合后续章节内容逐步更新)

相关链接:

全平台轻量开源verilog仿真工具iverilog+GTKWave使用教程

[CSDN 上 vcd 文件]( https://blog.csdn.net/github_33678609/article/details/86575328 )

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1