Anlogic Serdes PRBS 环路测试

本实验以 PRBS 产生测试数据,用于验证 Serdes 部分硬件电路是否正常工作 。

1.硬件电路

PH1A90有两个Serdes BANK 分别为BANK82 和BANK 83。需要注意的是该开发板Serdes引出到SFP的是Channel1,引出到FMC的是Channel0。

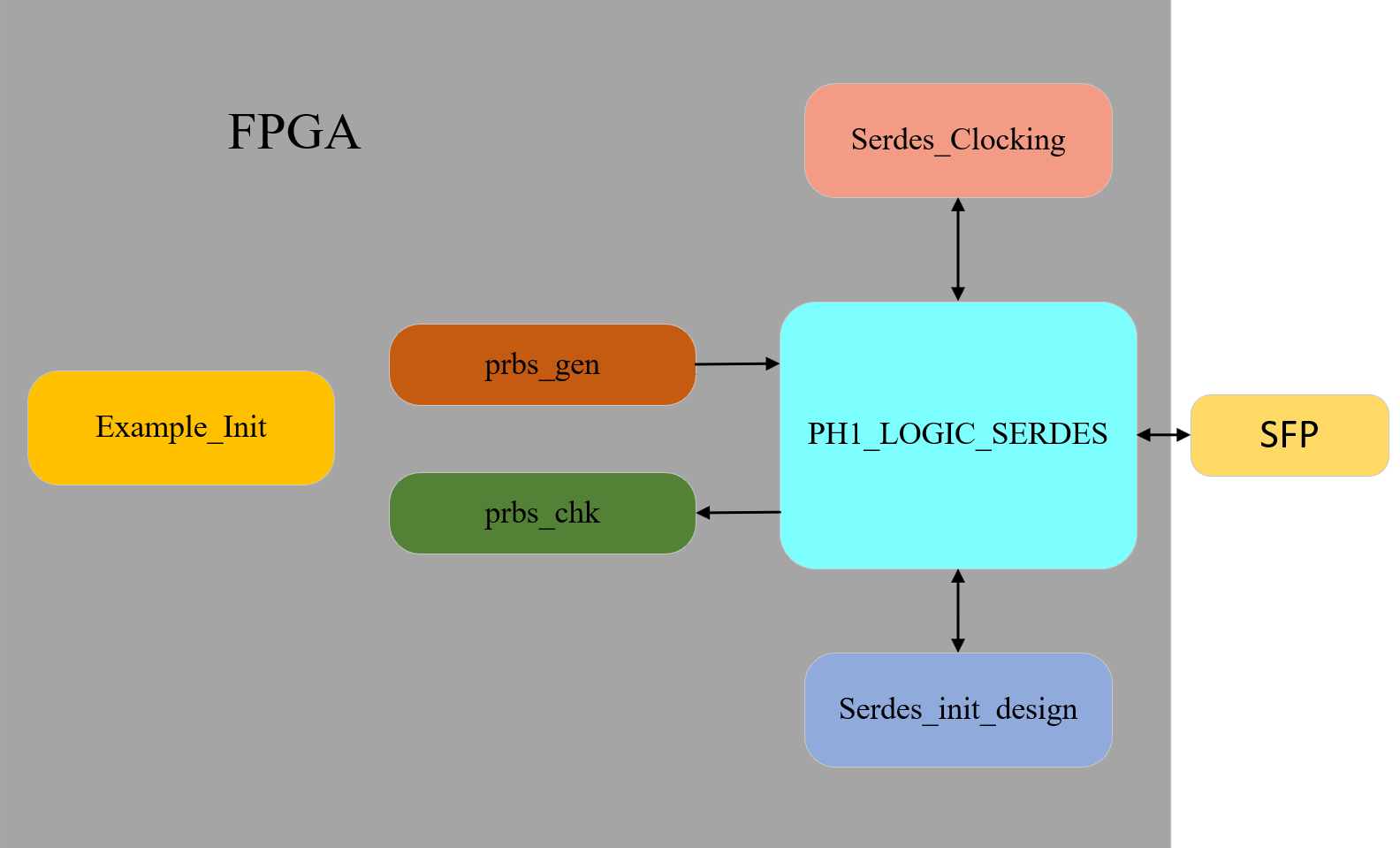

2.系统框图

Serdes 的应用需要外围电路的辅助,以 PH1 logic serdesIP 为核心,配以时钟模块和初始化模块,为了验证基本的 serdes 的建链与数据收发外部进行 prbs(伪随机码常用于高速串行通信的通道验证)数据的生成与校验。

3.FPGA 默认配置

在上板测试前先看本示例公测默认的SERDES IP配置信息。

3.1 本参考示例工程的默认SERDES IP配置

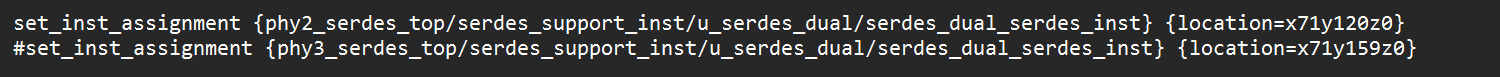

PH1A90 有 2 个 BANK 的 SERDES,分别是 BANK82 和 BANK83,软件 IP 中的位置为: 🙁 x71y120z0, x71y159z0 ) 。本次实验中仅使用BANK 82的Channel1。因此使用TD5.6.2打开SERDES IP 图形界面,配置如图所示。

Protocol and dual 页面

PCS界面

PMA界面

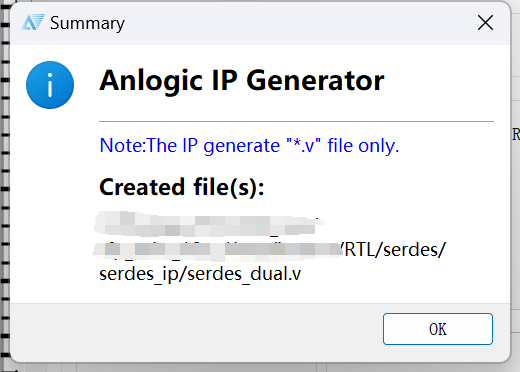

默认配置下不需要修改,若需要更新SERDES IP配置,对SERDES IP进行更新配置之后,点击OK。

弹出该界面继续点击OK。重新生成IP。

打开工程路径下的/RTL/serdes/serdes_ip/serdes_dual_src.v文件,打开工程路径下的define.v文件,将serdes_dual_src.v文件中的宏定义赋值到define.v中。注意复制替换部分为:`timescale上的所有部分。

完成后更新配置就已经替换到了本示例工程里了。

3.2代码中时钟选择设置

REF_REPEAT_CLK_EN:

使 能 参 考 时 钟 复 制 功能 , 用于参考时钟共享 。设置1表示需要共享使用其他BANK的时钟 。REF_CLK_UP_DOWN参数用于设置1需要共享的参考时钟位置是来自上方还是下方。

REF_CLK_UP_DOWN:

参考时钟共享时参考时钟来源选择,合法设置包括“UP”和 “DOWN”,当参考时钟共享自本 SERDES DUAL 位置上方时,设置 为“UP”,从本 SERDES DUAL 位置下方来时,设置为“DOWN”,当 REF_USE_PAD 为 0 时该属性有效。默认值设置为“UP”,推荐使 用 IP Generator 产生的值。该属性仅在 PH1A90 器件生效。

REF_CLK_MUX_EN:

默认值 1’b0。当使用 BUFG 驱动参考时钟时,设置为 1’b1,其他情况下设置为 1’b0,推荐使用 IP Generator产生的值。

REF_USE_PAD:

选择参考时钟由外部管脚提供还是内部提供。接 1 使用外部管脚做参考时钟。接 0 使用内部提供的参考时钟。默认值为 0。推 荐使用 IP Generator 产生的值。

BANK 82 时钟参数设置如下:

3.3 更新SERDES DUAL

在使用PH1A90 器件时,默认使用BANK 82对应的SERDES DUAL。如果需要新增或者切换。步骤如下:

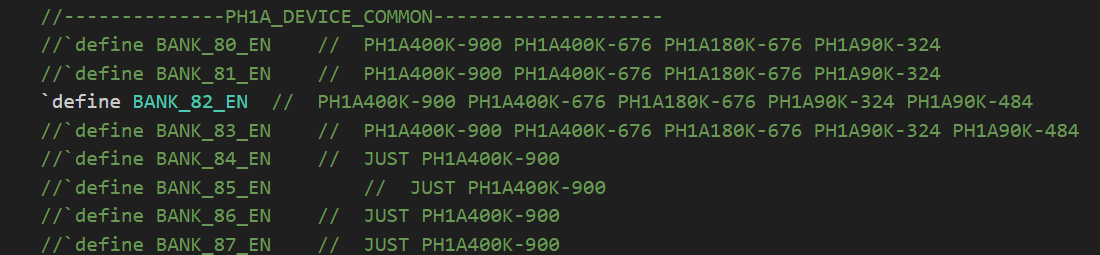

1.根据需要修改define.v文件 对BANK 进行使能

2.之后进行对应的BANK 的adc约束进行修改。

3.4NCS23345配置

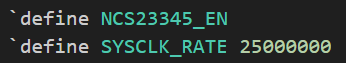

在define.v文件里进行定义使能

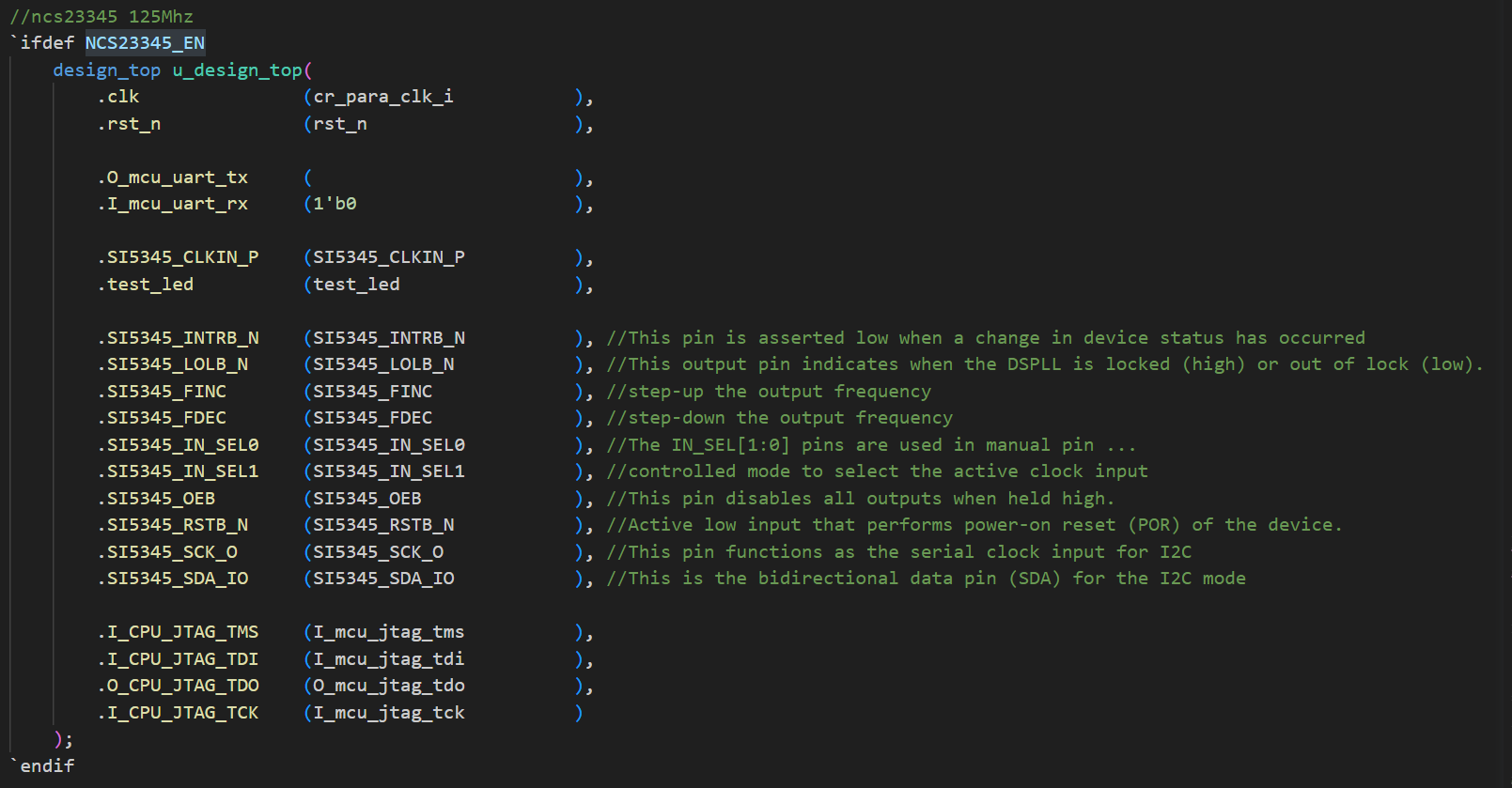

multi_dual_top文件中已经对NCS23345配置程序进行了条件例化。

4.FPGA 上板测试步骤

1.硬件连线完成后进行bit文件下载。可以看到加载完成后,l1_data_locked 信号会拉高(LED7 亮),表示Lane1的数据校验正确。

2.数据校验成功并保持一段时间后,link_status_out会拉低(LED8灭),表示建链成功。

3.link_down_latched_out仍为低电平(外接LED灭),需要手工清除 ,这是因为上电初始化过程中是不能建链的,是正常现象。

4.手动清除是信号phy_link_down_latched_reset_in(SW3按键),清除历史错误后外接LED点亮。

5.出现乱码(按下按键SW2注入错误或断连SFP模块)则信号l1_data_locked(LED7) 拉低锁存建链失败历史信息。过程为 link_status_out(LED8)拉高表示链路不正常。 link_down_latched_out (外接LED)拉低表示建链失败历史信息。

数据恢复正常后l1_data_locked (LED7)自动拉高。

过了若干周期,link_status_out (LED8)拉低表示建链恢复正常,而link_down_latched_out(外接LED) 仍为低电平表示存在建链失败的历史,直至按下SW3清除历史信息。

至此Anlogic Serdes PRBS 环路测试成功。

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1