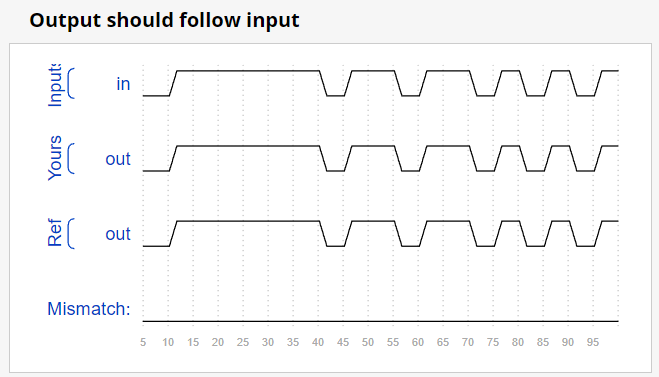

1、Simple wire

wire是verilog中的一种数据类型,可以看成是单向的导线,wire型可用于assign的赋值,通过assign声明语句从模块的输入流向模块的输出。verilog程序模块中的输入、输出信号类型默认自定义为wire型。assign赋值是“连续的”,右侧的值发生变化时左边的值立马发生变化。当存在多个assign语句时,assign出现的顺序和位置不影响,它们是并行运行的。

题目:

实现上图的连线。

代码:

module top_module( input in, output out );

assign out=in;

endmodule

结果:

输出与输入相同,输入一旦改变,输出立刻随之改变。

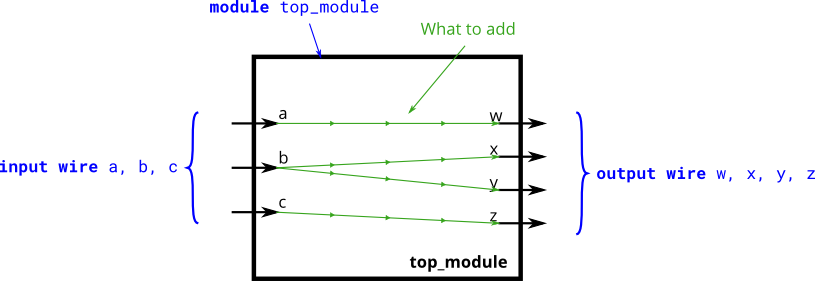

2、Four wires

题目:

创建一个包含3个输入以及4个输出的模块,并实现图中的连线。

代码:

其中assign语句的顺序可以改变,这四条语句同时运行。

module top_module(

input a,b,c,

output w,x,y,z );

assign w=a;

assign x=b;

assign y=b;

assign z=c;

endmodule

结果:

w值与a值相同,x、y值与b值相同,z值与c值相同。

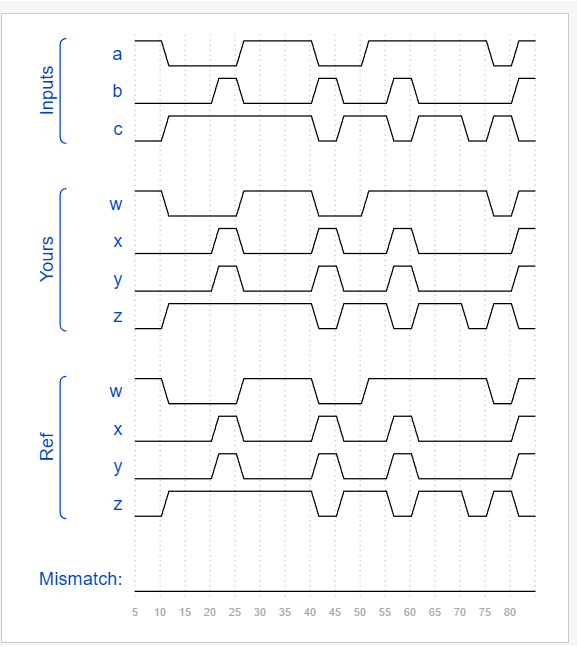

3、Inverter

题目:

创建一个模块实现非门,使用一个assign语句将持续地把in的反值驱动到out。

下表总结常用的位运算符:

| 运算符 | 作用 |

|---|

| ~ | 取反(NOT) |

| & | 按位与(AND) |

| | | 按位或(OR) |

| ^ | 按位异或(XOR) |

| ~^ | 按位同或(XNOR) |

下表总结常用的逻辑运算符:

代码:

module top_module( input in, output out );

assign out=~in;

endmodule

结果:

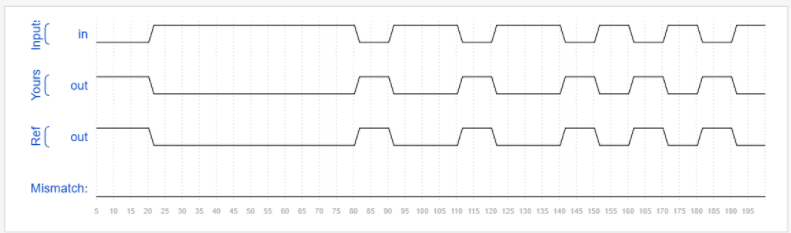

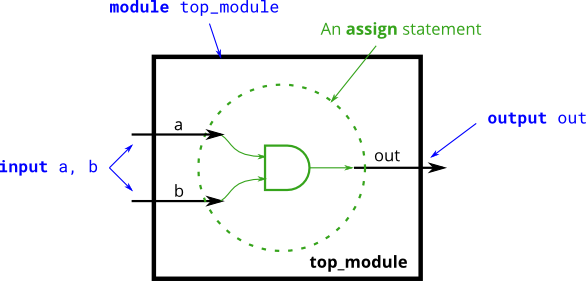

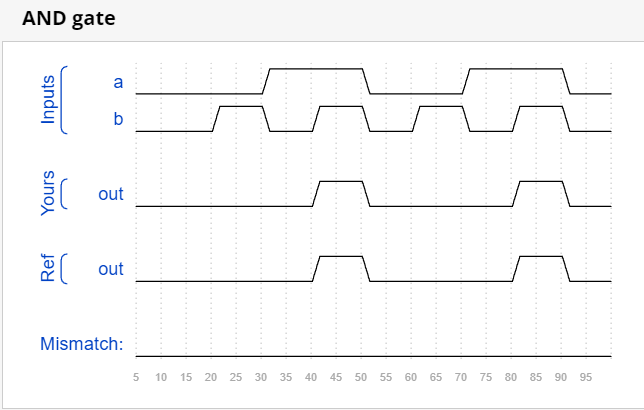

4、AND gate

题目:

创建一个模块实现与门,使用一个assign语句实现该功能。

代码:

module top_module(

input a,

input b,

output out );

assign out=a&b;

endmodule

结果:

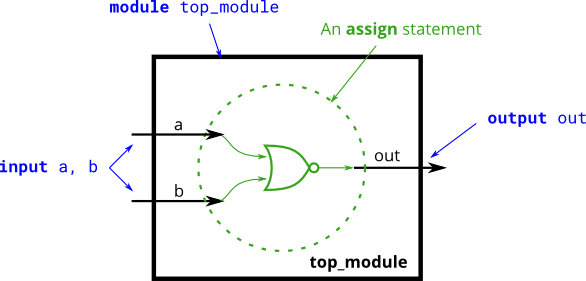

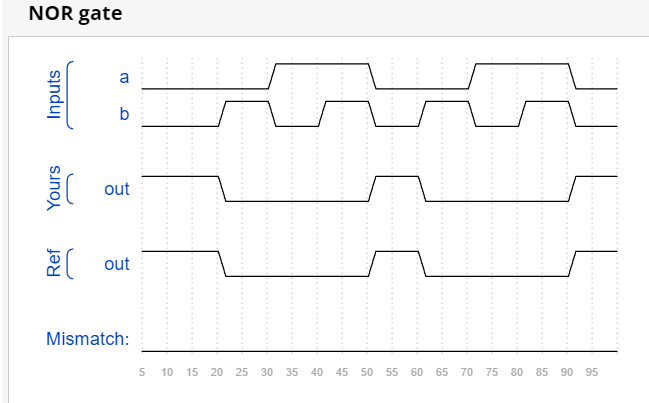

5、NOR gate

题目:

创建一个模块实现或非门,使用一个assign语句实现该功能。

代码:

module top_module(

input a,

input b,

output out );

assign out=~(a|b);

endmodule

结果:

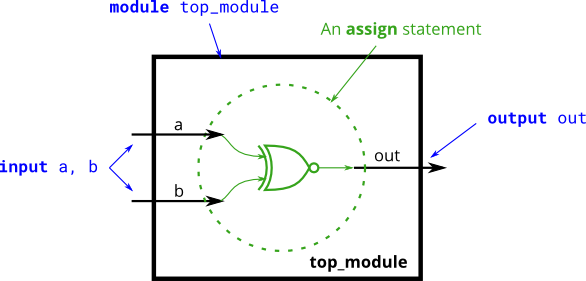

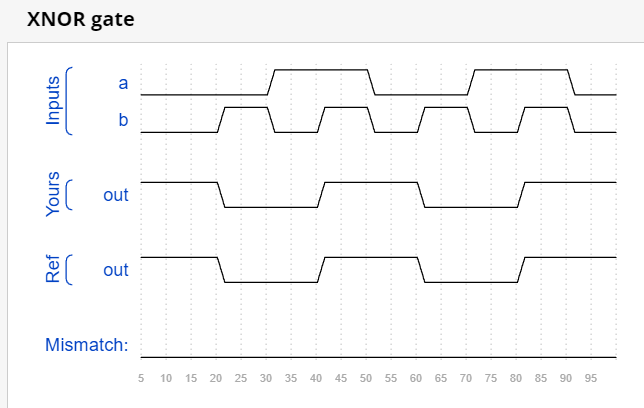

6、XNOR gate

题目:

创建一个模块实现同或门,使用一个assign语句实现该功能。

代码:

module top_module(

input a,

input b,

output out );

assign out=~(a^b);

endmodule

结果:

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1