我这两天在 YADAN Board 上写一个 Verilog 项目,代码能被综合完成并烧写到开发板上,但开发板就是无法展示预期的现象。今天检查了一天,终于发现了问题:

- 在项目中,模块 A 和模块 B 本应通过线 C 相连,而我忘记声明 wire C 了。

我加上 wire C 的声明,重新综合和烧写,最终观察到了预期的现象。

但是,为什么我不声明 wire C,IDE 也能综合完代码并生成最终的 .bit 文件呢?这其实是 Verilog 的语法特性,Verilog 自 2001 版本开始支持使用 隐式的线 (Implicit wire) 来连接模块,这一特性一定程度上能简化代码,提高可读性,不过如果使用不当,可能无法保证最终的现象。

我写了如下模块来测试,可以发现,代码中并没有显式地声明 temp 这根线:

module wire_bug_test_top(input A,

input B,

output C);

nand_gate nand_gate_0(

.in_A(A),

.in_B(1'b1),

.out(temp)

);

nand_gate nand_gate_1(

.in_A(temp),

.in_B(B),

.out(C)

);

endmodule

将这份代码分别丢给四款不同的 HDL IDE,它们都能成功综合这个模块,并实现与预期一致的实验效果。其实,类似这样的描述清晰的单位宽 wire 通常是安全的,而在本文开头提到的那个项目里边导致问题的 Implicit wire 并非是如此理想的一根单位宽 wire。

那么,各个 IDE 能否提醒用户是否存在隐式的线呢?

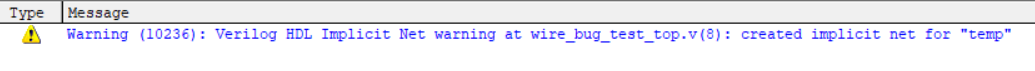

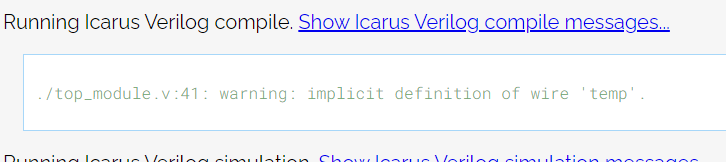

Vivado (2020.1) 和 Anlogic TD (4.6.6_SP1) 不会提醒,而 Quartus II (9.0) 和 Icarus Verilog (在 HDLBits 在线运行) 会分别报出如下两张图所示的 Warning。

参考资料 & 更多相关阅读

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1