开发必备硬件工具:

- Artix 7 开发板 x 1

- CKLINK

- USB 串口模块

- PMOD 模块 (根据设计需求自拟)

开发必备软件工具:

原始工程样例代码 (文件夹名称):

- Wujian100 (Vivado 工程,本文档中统一简称 FPGA 工程

- sdk (wujian100 对应 CDK 示例工程,本文档中统一简称 sdk 工程

辅助资料:

打开 ..\wujian100\wujian_n4 下的 vivado 工程

对 .xdc 文件进行修改,以满足相应的开发需求,打开串口配置管脚和相应的 GPIO 管脚:

set_property PACKAGE_PIN G16 [get_ports PAD_USI0_SCLK ] #RXD

set_property PACKAGE_PIN F16 [get_ports PAD_USI0_SD0 ] #TXD

修改约束后重新对 FPGA 工程进行综合与 .bit 文件生成,烧写至 N4DDR 开发板中。

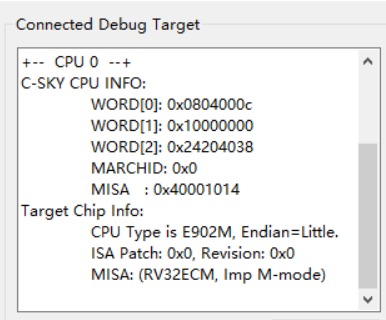

使用用于调试器 CKLINK 与 FPGA 开发板进行连接,进入 CDK 软件在 Project Setting 的 Debug 选项的 Target 窗口可以查看到 wujian100 的内核,如图 1 所示。

连接关系如下表所示

| FPGA | CKLINK |

|---|

| JA1: C17 | TCLK |

| JA2: D18 | TMS |

| GND | GND |

由于没有针对 N4DDR 上的 Flash 驱动,因此不能直接通过下载实现程序的运行,使用用于调试的 CKLINKB 通过分步调试后全速运行,实现程序暂存于 wujian100 的 RAM 中实现运行。各外设的使用 CDK 样例见原始工程样例代码的 sdk 压缩包。

CDK 工程方面以 UART 驱动为例,UART 的工程路径为: ..\sdk\projects\examples\driver\usart\CDK 如果使用的是本次的示例 wujian100 FPGA 工程,则默认的 wujian100 工作频率为 18 MHz,首先需要在 soc.h 文件中修改相应的时钟频率参数,代码如下:

#ifndef IHS_VALUE

#define IHS_VALUE (18000000)

#endif

#ifndef EHS_VALUE

#define EHS_VALUE (18000000)

#endif

使用函数接口 csi_usart_config() 便可实现相应的配置,接口函数的参数如下:

int32_t csi_usart_config(usart_handle_t handle,

uint32_t baud,

usart_mode_e mode,

usart_parity_e parity,

usart_stop_bits_e stopbits,

usart_data_bits_e bits)

推荐配置如下:

csi_usart_config(usart, 115200, USART_MODE_ASYNCHRONOUS, USART_PARITY_NONE, USART_STOP_BITS_1, USART_DATA_BITS_8);

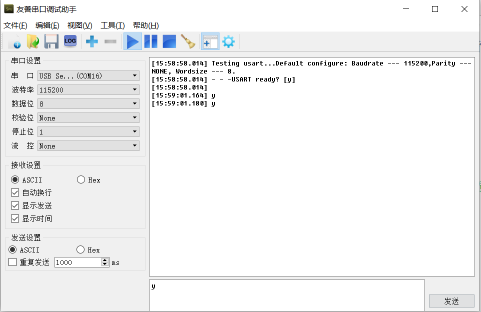

在此波特率下,编译工程,通过 USB 串口模块或者 PMOD UART 模块与电脑进行连接,使用 CKLINKB 在调试模式下全速运行。打开电脑的串口助手软件,可以看到以下现象,如图 2 所示:

网站备案号:ICP备16046599号-1

网站备案号:ICP备16046599号-1